Examen Final Convocatoria 1 8-Febrero-2011

Apellidos, Nombre:

Problema 1. En una empresa se requiere implementar la siguiente función lógica:

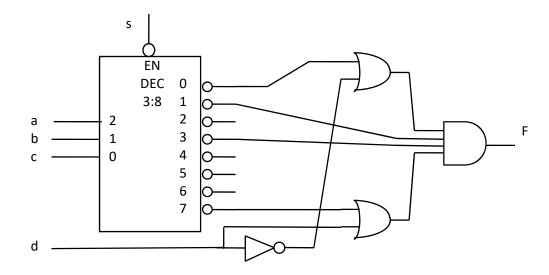

$$f(a, b, c, d) = \Sigma(0, 4, 5, 8) + d(1, 2, 10, 12, 14)$$

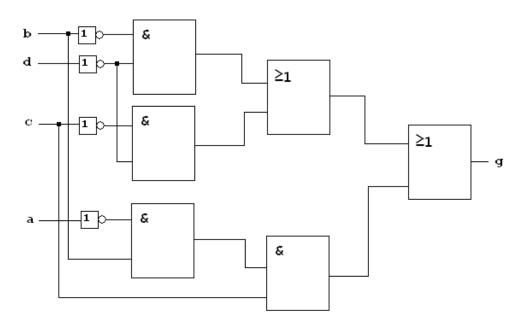

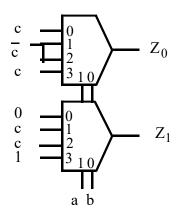

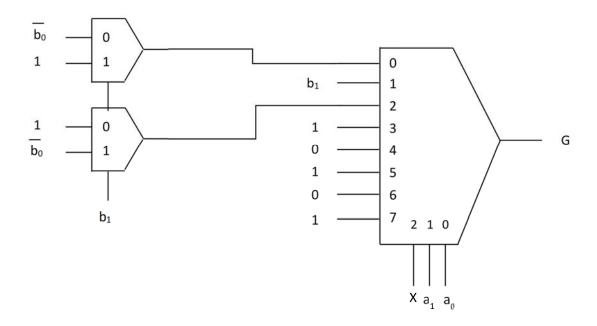

Para ello, el equipo de diseño de circuitos electrónicos de la empresa ha propuesto la siguiente solución:

Un alumno de Ingeniería de Computadores en prácticas en esa empresa percibe que la solución aportada no es buena.

Para comprobar si usted comienza a tener competencias parecidas a las de ese alumno, se le pide:

- a. Represente el K-mapa de la función representada en el circuito de la figura, g.

- b. Represente el K-mapa de la función objetivo, f.

- c. Indique, si las hay, en qué combinaciones de entrada de la función g se han cometido errores en relación a la función original f.

- d. Implemente la función f con un circuito lógico mínimo **en dos niveles** (hipótesis de doble raíl) empleando cualquier tipo de puertas.

#### Apellidos, Nombre:

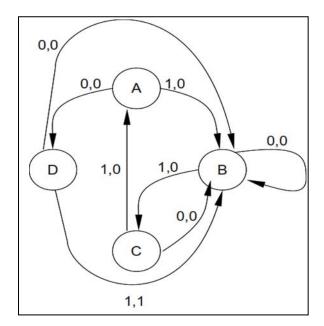

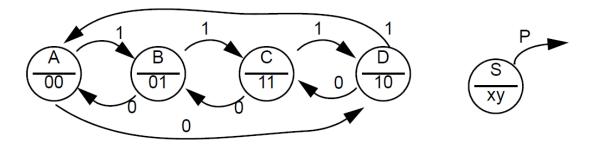

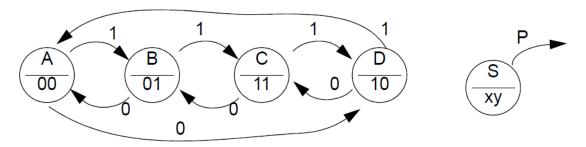

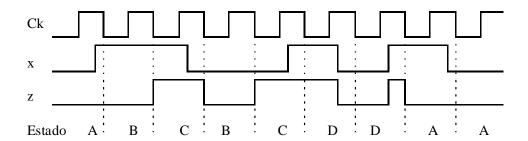

Problema 2. Dado el diagrama de estados de la figura, responda de forma justificada a lo siguiente:

a) Obtenga la secuencia de estados y de salida suponiendo que la entrada va tomando sucesivamente los valores:

X: 0, 0, 1, 0, 0, 1, 1, 0, 1, 1, 0, 1, 0, 1, 1, 1

Suponga también que inicialmente se encuentra en el estado A.

- b) Explique en pocas palabras qué función realiza esta máquina de estados.

- c) Dibuje el diagrama de estados de una máquina equivalente por el modelo de MOORE.

#### SOLUCIÓN caso a):

#### Apellidos, Nombre:

Problema 3. Se dispone de contadores mod-10 (cuentan de 0 a 9) con las siguientes características:

- Señal de puesta a cero síncrona (CLEAR) activa en alto.

- Señal de cuenta ascendente (UP) activa en alto.

- La señal CLEAR tiene prioridad.

- Los contadores NO DISPONEN de salida de carry.

- a. Dibuje este contador como un bloque (esto es, descríbalo a nivel estructural) y dé su tabla de operación a nivel RT (descripción funcional).

- b. Construya un contador BCD módulo 100.

- c. Construya un contador BCD módulo 25.

#### **Examen Final**

#### Convocatoria 2

# 8-Septiembre-2011

#### Apellidos, Nombre:

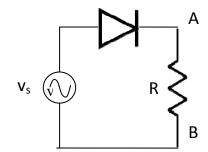

Problema 1. La figura representa una pequeña variación del circuito recortador del problema Tema2.P1.

Si  $v_s$  = 10.sen  $\omega t$  y R =1k $\Omega$ , dibuje la caída de tensión en el diodo y la onda de salida ( $v_{AB}$ ) en cada uno de los casos siguientes para el modelo de diodo:

- a. Ideal.

- b. Batería. Use 0,7 V.

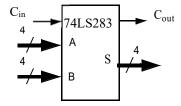

#### Problema 2.

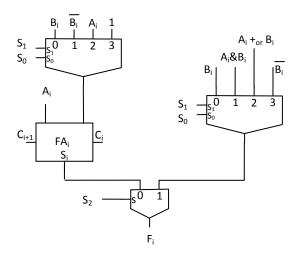

a) Diseñe un circuito con dos variables de selección que genere las siguientes operaciones aritméticas.

| <b>S1</b> | <i>50</i> | F       |

|-----------|-----------|---------|

| 0         | 0         | A + B   |

| 0         | 1         | 2 A + 1 |

| 1         | 0         | A – B   |

| 1         | 1         | 3 A     |

Nota: A y B son números de 4 bits en Ca2.

b) Realice la operación (-12.75) + 14.41 en Ca2 utilizando 10 bits para cada número. Tres de estos bits son para la parte fraccionaria. Compruebe los posibles errores.

# Problema 3.

CED - GII-IC

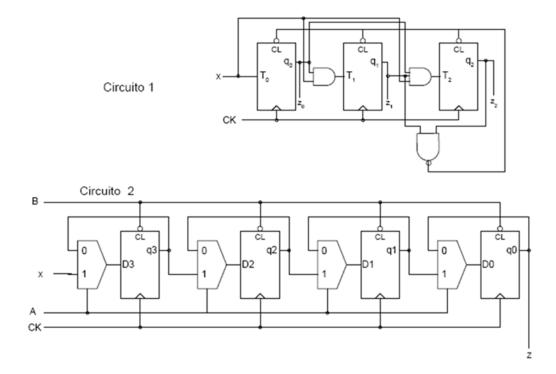

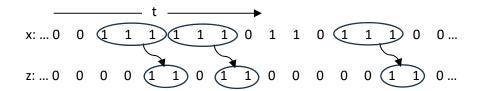

Se dispone de una línea de transmisión síncrona X por la que llegan datos en serie. Con un circuito secuencial se pretende controlar los últimos tres bits llegados: la salida Z será 0 si en los últimos tres bits, la mayoría son 0's mientras que será 1 si la mayoría son 1's. Por ejemplo, ante la secuencia de entradas dada (X), obtenemos la secuencia de salida (Z) siguientes:

X: 10100011

Z: - - 1 0 0 0 0 1

Se pide:

- a) Dibuje el diagrama de estados del circuito.

- b) Aplique la secuencia de entradas del ejemplo anterior a su diagrama de estados y obtenga las secuencias de cambios de estado y de salida correspondientes. Verifique si su diagrama de estados del apartado a) funciona como indica el ejemplo del enunciado.

- c) Diseñe el circuito con biestables T y puertas.

NOTA: Tanto el diagrama de estados como el circuito deben ser lo más simples posibles.

Examen Final Convocatoria 3 07-diciembre-2011

Apellidos, Nombre:

Problema 1. Un sistema que mide periódicamente la temperatura de un experimento de laboratorio da la información utilizando números de 4 bits en notación complemento a dos (Ca2).

- a. Escriba la tabla de todas las temperaturas posibles, dando su valor decimal y el correspondiente valor binario en notación Ca2.

- Diseñe un circuito que detecte el intervalo cerrado de códigos [-5,4] utilizando exclusivamente dos comparadores de magnitud de 4 bits y puertas de dos entradas.

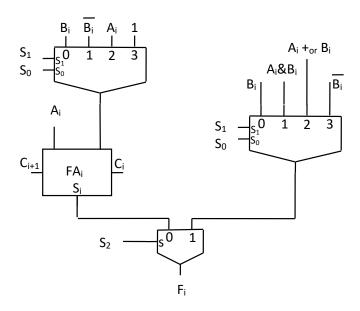

Problema 2. Diseñe la etapa típica de un circuito aritmético que responda a la siguiente tabla.

| S1 S0 | Cin = 0   | Cin = 1     |

|-------|-----------|-------------|

| 0 0   | A + B     | A + B + 1   |

| 0 1   | 2·A + B   | 2·A + B + 1 |

| 1 -   | B – A – 1 | B – A       |

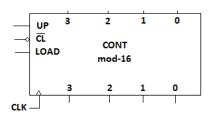

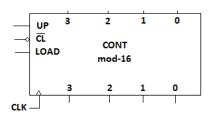

Problema 3. Obtenga un contador módulo 5 de coste mínimo, que cuente desde 4 a 8, usando contadores como el de la figura y puertas.

| CL | LOAD | UP | OPERACIÓN        | TIPO      |

|----|------|----|------------------|-----------|

| 0  | -    | -  | CONT <- 0        | asíncrona |

| 1  | 1    | -  | CONT <- X        | síncrona  |

| 1  | 0    | 0  | CONT <- CONT     | síncrona  |

| 1  | 0    | 1  | CONT <- CONT + 1 | síncrona  |

**Examen Final**

Convocatoria 1

**3-Febrero-2012**

#### Apellidos, Nombre:

Problema 1. Se dispone de un número con signo de 3 bits codificado en Signo-Magnitud cuando una entrada x es 0 y en Complemento a 2 si x es 1. **Manteniendo el código de entrada**, se desea transformarlo según las siguientes reglas:

- a. Si el número es positivo, se le resta 2.

- b. Si el número es negativo, se le suma 2.

- c. Si el número es cero, debe salir cero.

- d. Obtenga las soluciones con sólo puertas NAND y con sólo puertas NOR (incluya, en su caso, las inespecificaciones que surjan), y elija el circuito óptimo correspondiente usando sólo un tipo de puertas. Indique cuál es el coste de la solución elegida así como en cuánto mejora a la otra solución.

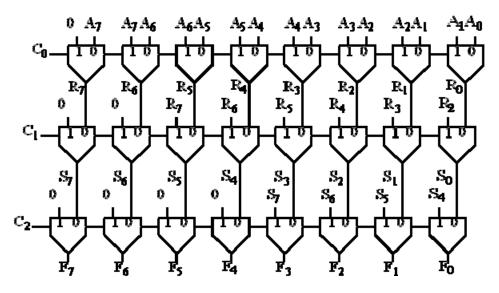

- Problema 2. a) Analice el circuito de la figura **y describa verbalmente** qué función realiza interpretando que  $A=A_7A_6A_5A_4A_3A_2A_1A_0$  es el dato de entrada (8 bits), que  $C=C_2C_1C_0$  es la señal de control (3 bits) y que  $F=F_7F_6F_5F_4F_3F_2F_1F_0$  es el dato de salida.

- b) Empleando el circuito anterior y Mux 2:1, diseñe un circuito que posea una señal de entrada más (SH) de forma que cuando SH=0 se realice el desplazamiento a la derecha del dato y cuando SH=1 se realice el desplazamiento a la izquierda.

#### Apellidos, Nombre:

Problema 3. Un circuito secuencial síncrono recibe, por sus líneas de entrada  $(X_1,X_0)$ , números binarios de 2 bits sincronizados con su señal de reloj. El circuito compara los bits recibidos en el ciclo de reloj actual con los que se recibieron en el anterior e indica por sus salidas  $(Z_1,Z_0)$  cuántos cambios de bits se han producido.

- a. Obtenga la tabla de estados/salida que refleje dicho comportamiento, correspondiente a un autómata de Mealy.

- b. Diseñe dicho autómata con biestables D y puertas lógicas

# Examen Final Convocatoria 2 11-septiembre-2012

Apellidos, Nombre:

Problema 1. Un sistema que mide periódicamente la temperatura de un experimento de laboratorio da la información utilizando números **de 4 bits en notación complemento a dos (Ca2).**

- a. Escriba la tabla de todas las temperaturas posibles, dando su valor decimal y el correspondiente valor binario en notación Ca2.

- Diseñe un circuito que detecte el intervalo cerrado de códigos [-5,4] utilizando exclusivamente dos comparadores de magnitud de 4 bits y puertas de dos entradas.

Problema 2. Diseñe la etapa típica de un circuito aritmético que responda a la siguiente tabla.

| S1 S0 | Cin = 0 | Cin = 1     |

|-------|---------|-------------|

| 0 0   | A + B   | A + B + 1   |

| 0 1   | 2·A + B | 2·A + B + 1 |

| 1 -   | B-A-1   | B – A       |

Problema 3. Obtenga un contador módulo 5 de coste mínimo, que cuente desde 4 a 8, usando contadores como el de la figura y puertas.

| CL | LOAD | UP | OPERACIÓN        | TIPO      |

|----|------|----|------------------|-----------|

| 0  | -    | -  | CONT <- 0        | asíncrona |

| 1  | 1    | -  | CONT <- X        | síncrona  |

| 1  | 0    | 0  | CONT <- CONT     | síncrona  |

| 1  | 0    | 1  | CONT <- CONT + 1 | síncrona  |

#### **Examen Final**

#### Convocatoria 3

### 5-diciembre-2012

#### Apellidos, Nombre:

#### Problema 1. Responda a las siguientes cuestiones:

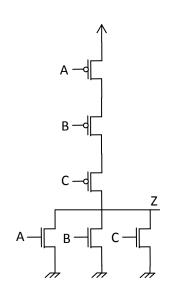

- a. Justifique razonadamente qué tipo de puerta lógica se muestra en la figura, obteniendo su tabla de verdad. (Use sólo 0's y 1's).

- b. Obtenga a nivel de transistores la puerta dual de la del apartado a y dibuje su símbolo estándar.

- c. Explique qué son:

- a. Half adder

- b. Full adder

- c. N-bits parallel adder

- d. Indique las diferencias y semejanzas entre un biestable D tipo disparado por nivel H y otro disparado por flanco positivo.

$$X = 1$$

$\Rightarrow$   $Z_{3-0} = Ca1(A_{3-0})$

$$X = 0$$

$\Rightarrow$   $Z_{3-0} = Ca2(A_{3-0})$

CED - GII-IC

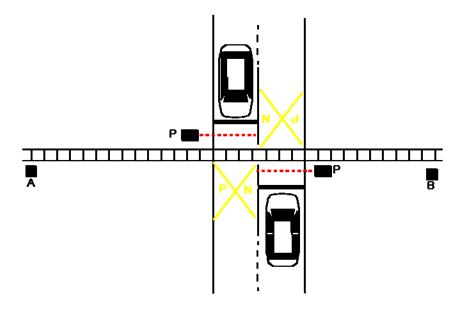

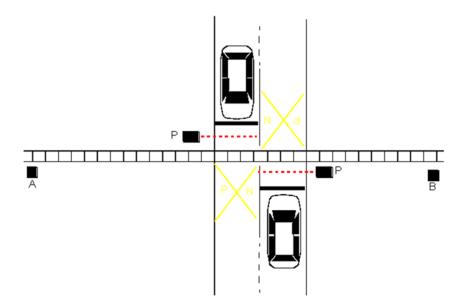

- Problema 3. Se desea controlar las barreras de un paso a nivel (ver figura). A cierta distancia del paso a nivel, y sobre la vía, existen un par de sensores que se activan al pasar el tren (A y B). No se sabe si el tren es más largo o más corto que la distancia que separa a ambos sensores. Pero sí se sabe que los trenes siempre pasan en la dirección de A a B y que no pueden venir dos trenes consecutivos con una separación inferior a la distancia AB.

- a. Obtener el diagrama de estados de la máquina de Mealy que controla la señal P que actúa sobre las barreras. P=0 equivale a barrera bajada.

- b. Implementar dicha máquina usando biestables D y puertas NAND.

NOTA: Los sensores A y B actúan de manera que están activados mientras el tren esté pasando sobre ellos.

Examen Final Convocatoria 1 30-enero-2013

Apellidos, Nombre:

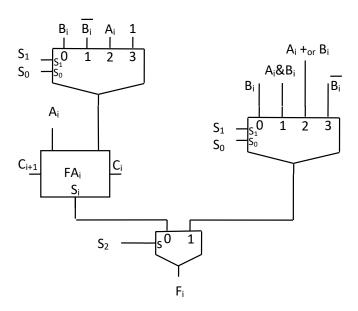

Problema 1. En la figura es representa un diseño de una etapa típica de una ALU similar, pero no igual, a la dada en clase. Los bits de salida de estado (Z, V, S y C<sub>out</sub>), que no están representados, se obtienen de forma similar.

- a. Obtenga razonadamente la tabla funcional.

- b. Considere que tiene dos datos P y Q con los que va a operar mediante esa ALU, con dimensiones de 8 bits. Indique los valores binarios de <u>todas</u> las entradas y de todas las salidas de la ALU para los dos casos siguientes:

- 1) Si P y Q son [P] = \$6C y [Q] = \$B5 y se suman (P+Q)

- 2) Si P y Q son [P] = \$6C y [Q] = \$B5 y se restan (P-Q)

- c. Si P y Q son dos números con signo (Ca2), interprete los resultados de los dos casos del apartado anterior y verifique si son correctos o no operando en decimal.

- d. Si P y Q son dos números sin signo (esto es, magnitudes), interprete los resultados de los dos casos del apartado anterior y verifique si son correctos o no operando en decimal.

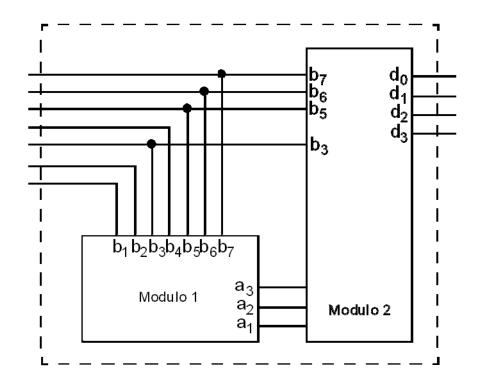

Problema 2. Los códigos de Hamming son un tipo especial de código que permiten, no sólo detectar errores, sino además corregirlos. Dada una palabra de 4 bits que queremos transmitir (d3, d2, d1, d0), es necesario añadir 3 bits (c3, c2, c1) destinados a la corrección de un error en un bit. Así la palabra trasmitida consta de 7 bits (b<sub>7</sub> a b<sub>1</sub>):

| b <sub>7</sub> | $b_6$          | $b_5$ | $b_4$          | $b_3$ | $b_2$          | $b_1$          |  |

|----------------|----------------|-------|----------------|-------|----------------|----------------|--|

| d <sub>3</sub> | d <sub>2</sub> | $d_1$ | C <sub>3</sub> | $d_0$ | C <sub>2</sub> | C <sub>1</sub> |  |

El código corrector se fabrica de la siguiente forma:

- c3: paridad par de los bits 4, 5, 6 y 7 (grupo 3) de la palabra transmitida.

- c2: paridad par de los bits 2, 3, 6 y 7 (grupo 2) de la palabra transmitida.

- c1: paridad par de los bits 1, 3, 5 y 7 (grupo 1) de la palabra transmitida.

Se desea diseñar el circuito que recupera la información en el receptor, suponiendo que puede fallar, como máximo un único bit (pudiendo ser cualquiera de los 7). Para ello se debe seguir el esquema de la figura.

- a. Diseñar el módulo 1 (detector de paridad), sabiendo que ai = 1 si la paridad del grupo i es incorrecta.

- b. Diseñar el módulo 2 sabiendo que el código formado por a3a2a1 indica, en binario natural, la posición del bit incorrecto, y 0 en caso de que no hubiera error. La salida d3d2d1d0 debe ser la palabra original corregida en caso de error.

Se dispone, para realizar el diseño completo, de un decodificador de 3 a 8 y puertas XOR de 2 entradas.

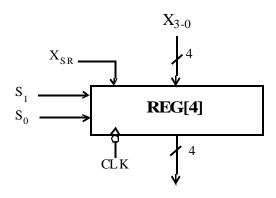

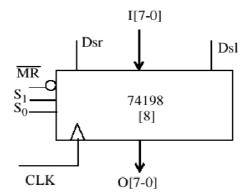

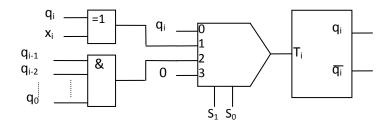

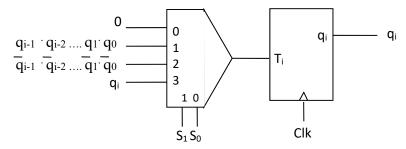

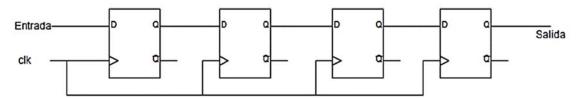

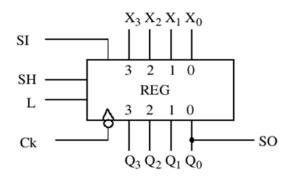

Problema 3. Se dispone de registros de 4 bits como el mostrado en la figura, puertas y subsistemas combinacionales.

- a. Diseñe un registro universal de 16 bits (esto es, con dos señales de selección de operación que permitan la inhibición, carga en paralelo, desplazamiento a izquierda y a derecha).

- b. Utilizando el registro universal de 16 bits, se desea generar bit a bit la secuencia de dígitos impares y primos en BCD (en decimal, 1, 3, 5 y 7). Realice este generador de secuencias indicando ordenadamente cómo debe trabajar. [Como verá, puede responder al apartado "b" sin haber hecho el "a"].

| $S_1 S_0$         | REG[4]                                                                                                                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0<br>0 1<br>1 - | $\begin{array}{c} \text{REG} \longleftarrow \text{REG} \\ \text{REG} \longleftarrow \text{X}_{3\text{-}0} \\ \text{REG} \longleftarrow \text{SHR} \left( \text{REG}, \text{X}_{\text{SR}} \right) \end{array}$ |

**Examen Final**

Convocatoria 2

9-septiembre-2013

Apellidos, Nombre:

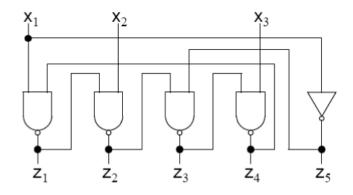

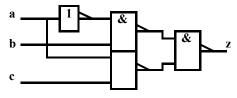

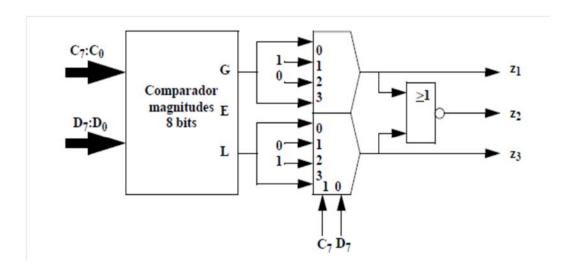

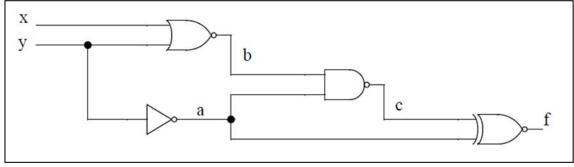

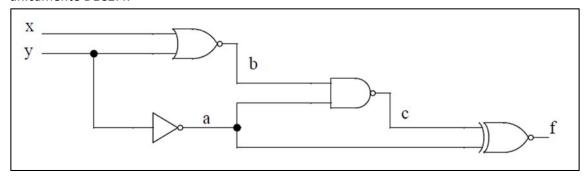

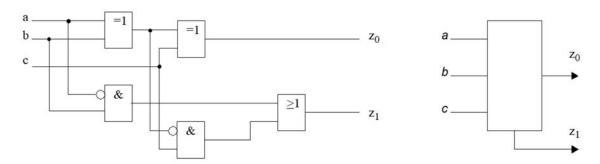

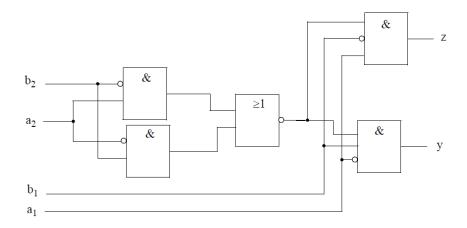

Problema 1. El circuito de la figura presenta realimentación, pero no es un circuito con memoria.

- a. Analícelo y encuentre las expresiones normalizadas de suma de productos para cada salida.

- b. Obtenga un diseño alternativo de z<sub>3</sub> usando puertas NAND.

- c. Obtenga un diseño alternativo de z<sub>2</sub> usando MUX4:1.

NOTA: No dispone de variables en doble raíl.

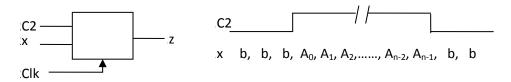

Problema 2. El circuito de la figura debe funcionar como complementador a 2, z=Ca2(x), de la siguiente forma. Cuando C2 sea 0 el circuito debe esperar dando salida 0. Cuando C2=1 por la entrada x se recibirá bit a bit un número A de "n" bits comenzando por su LSB, A0 (ver figura). Por z deberá ir saliendo, también bit a bit, el Ca2 de A.

Diseñe este circuito con biestables JK y puertas.

(<u>Idea:</u> Recuerde que se puede realizar el Ca2 si 'se dejan los 0's y el primer 1 menos significativos y se complementan el resto de bits'.)

Problema 3. Se dispone de un registro M de 16 bits con salidas de datos en paralelo, señal de lectura R activa en alto (cuando R está inactiva, las salidas de M toman el valor 0) y dos señales de selección de operación  $A_1A_0$  con las siguientes funcionalidades:

$A_1A_0 = 00$ : Desplazamiento lógico a la derecha (entra 0)

$A_1A_0 = 01$ : Desplazamiento aritmético a la derecha (entra bit de signo)

$A_1A_0 = 10$ : Rotación a la derecha

$A_1A_0 = 11$ : No operación (inhibición)

- a. Describa a nivel RT el registro M como un bloque. Debe dar la descripción estructural y la funcional mediante lenguaje RT.

- b. Suponiendo que inicialmente el registro contiene el dato \$AAAA (\$ denota hexadecimal), indique qué ocurre para la siguiente secuencia de entradas (cada valor corresponde a un ciclo de reloj):

$R A_1 A_0 =$

0 - 0,

110,

011,

001

100

c. Diseñe el registro utilizando las puertas necesarias y el 74198 (véase figura).

| $\overline{MR}$ $S_1$ $S_0$ |                      |

|-----------------------------|----------------------|

| 0                           | Puesta a 0 asíncrona |

| 1 0 0                       | Inhibición           |

| 1 0 1                       | Shift Left           |

| 1 1 0                       | Shift Right          |

| 1 1 1                       | Carga en Paralelo    |

| <b>Examen Final</b> | Convocatoria 1 | 24-enero-2014 |

|---------------------|----------------|---------------|

|                     |                |               |

| Apellidos, Nombre:  |                |               |

Problema 1. En el planeta Siur del sistema del gran sol de Pollux se disfruta de paz en todos sus rincones. Para los pocos casos de *siuritas* antisociales que hay, se dispone en Siur de un solo *lugar de reinserción social*, que cuenta con dos celdas, cada una con capacidad para tres *siuritas* como máximo. Desde hace ya mucho tiempo hay cuatro *siuritas* que deben estar recluidos permanentemente pues son antisociales crónicos a los que no se ha conseguido reinsertar. Se trata de Asclat, Bruki, Cirto y Dremx.

Por motivos de capacidad no pueden estar todos en la misma celda y por motivos terapéuticos y psicológicos debe cambiar su distribución cada poco tiempo. Sin embargo no pueden estar de cualquier manera. Las relaciones entre ellos hacen que sea extremadamente peligroso encerrar en la misma celda a Asclat y Dremx si no está presente también Cirto. También es peligrosísimo que estén juntos Bruki y Asclat salvo que con ellos dos se encuentre Cirto.

A usted se le solicita que **obtenga la función F que indique (con F=1) cuándo se ha elegido una distribución correcta** de esos cuatro *siuritas* en las celdas.

También debe **encontrar la expresión mínima en suma de productos y en producto de sumas** de F.

**Notas:** Es imprescindible que defina claramente sus variables y sus valores lógicos. No es necesario dibujar el circuito.

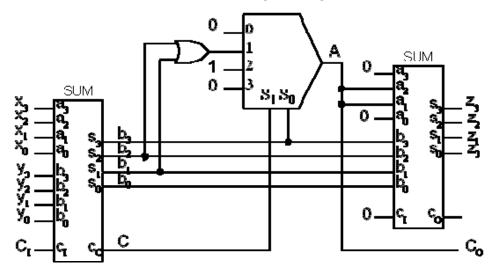

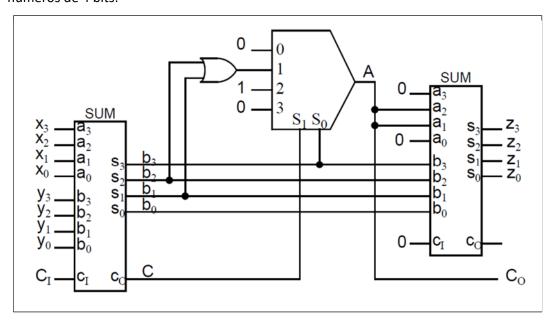

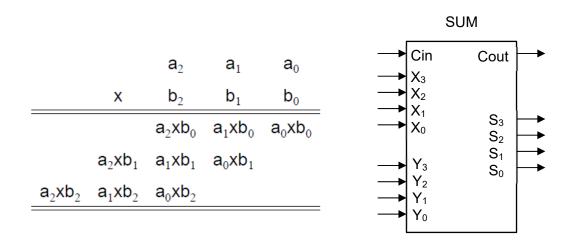

Problema 2. Considere el circuito de la siguiente figura.

- a. Obtenga la tabla de verdad de A=f (b<sub>3:0</sub>, C).

- b. Sabiendo que, en el circuito de la figura, los módulos SUM son sumadores paralelos de dos números de 4 bits, analice el funcionamiento del mismo y rellene la tabla siguiente.

| X <sub>3:0</sub> | <b>y</b> <sub>3:0</sub> | Cı | b <sub>3:0</sub> | С | Α | Z <sub>3:0</sub> | Co |

|------------------|-------------------------|----|------------------|---|---|------------------|----|

| 0111             | 0010                    | 0  |                  |   |   |                  |    |

| 0111             | 0010                    | 1  |                  |   |   |                  |    |

| 0111             | 0011                    | 0  |                  |   |   |                  |    |

| 1001             | 1001                    | 1  |                  |   |   |                  |    |

c. Si  $x_{3:0}$  e  $y_{3:0}$  son números BCD, indique la función del circuito de la figura.

Problema 3. Utilizando biestables JK disparados por flanco positivo y puertas lógicas, diseñe un circuito de Mealy con dos entradas, X e Y, y una salida Z la cual se debe activar cuando se reciben 2 ceros consecutivos en Y si X es 0 y cuando se reciben 2 unos consecutivos en Y si X es 1. (Los valores pueden solaparse; cada vez que X cambie se inicia la detección de la secuencia en Y).

a. Determine la secuencia de salida ante la siguiente secuencia de entrada:

| XY: | 01, 01, 11, 10, 11, 11, 11, 01, 00, 01, 00, 00 | , 01 |

|-----|------------------------------------------------|------|

| Z:  |                                                |      |

- b. Obtenga el grafo y la tabla de estados-salida que resuelva este problema, identificando el significado de cada estado de su respuesta.

- c. Compruebe si la tabla de estados que haya obtenido en el apartado anterior es correcta, determinando la secuencia de estados y de salida para la siguiente secuencia de entrada:

| XY: | 01, 01, 11, 10, 11, 11, 11, 01, 00, 01, 00, 00 |

|-----|------------------------------------------------|

| S:  |                                                |

| Z:  |                                                |

d. Obtenga el circuito deseado. (Es imprescindible mostrar las sucesivas etapas del proceso de diseño).

Examen Final Convocatoria 2 5-septiembre-2014

| Apellidos, Nombre: |  |

|--------------------|--|

|--------------------|--|

Problema 1. Para la función  $F(A, B, C, D) = \Pi(0, 1, 2, 3, 4, 6, 8, 9, 11, 14) \cdot \phi(5, 12),$

- a. Bajo la hipótesis de entradas en doble raíl, obtenga la **solución óptima en dos niveles**, usando **un único tipo** de puertas.

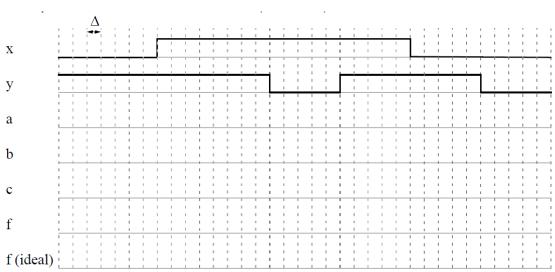

- b. Obtenga justificadamente la **forma de onda de la salida F** de su circuito para las excitaciones de entrada de la figura. Suponga que cada puerta tiene un retraso unidad (como valor aproximado, considere que el pulso más estrecho de los dibujados en el cronograma, el de "d", tiene una anchura de 4 unidades).

- c. Obtenga un diseño alternativo usando un único MUX4:1 para obtener F. Puede utilizar, además, las puertas lógicas que necesite. (Recuerde que la reducción de costes siempre es un criterio de diseño).

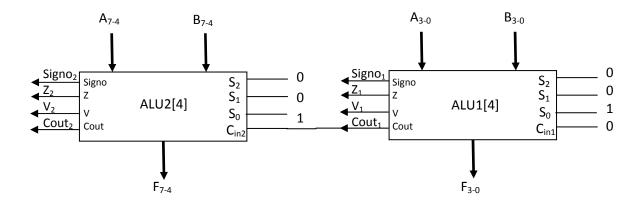

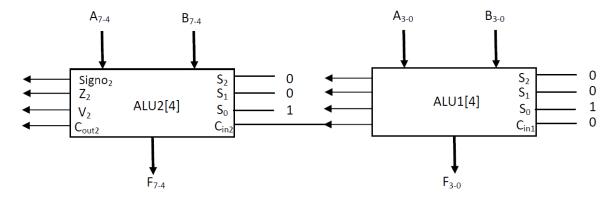

Problema 2. Se dispone de dos ALUs de 4 bits idénticas a las estudiadas en teoría conectadas como se muestra en la figura.

Tras la operación efectuada con los datos A y B de 8 bits se observan los siguientes valores en las líneas de salida de cada una de ellas:

| $C_{out2} = 0$             | C <sub>out1</sub> = 1      |

|----------------------------|----------------------------|

| V <sub>2</sub> = 1         | V <sub>1</sub> = 1         |

| $Z_2 = 0$                  | $Z_1 = 0$                  |

| S <sub>2</sub> = 1         | S <sub>1</sub> = 0         |

| F <sub>7-4</sub> = 1 0 1 0 | F <sub>3-0</sub> = 0 0 1 1 |

- a. Si A y B son números con signo (Ca2), ¿es el resultado F<sub>7-0</sub> correcto? Razone justificadamente la respuesta utilizando las salidas de las ALUs.

- b. Proponga unos valores binarios para A y B que den los resultados de salida indicados anteriormente.

- c. Haga su comprobación en decimal.

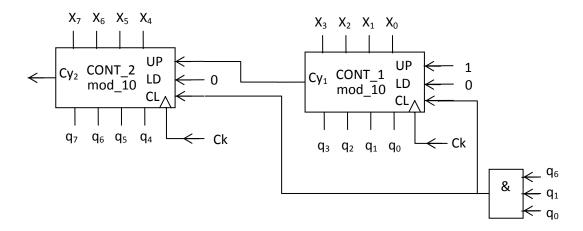

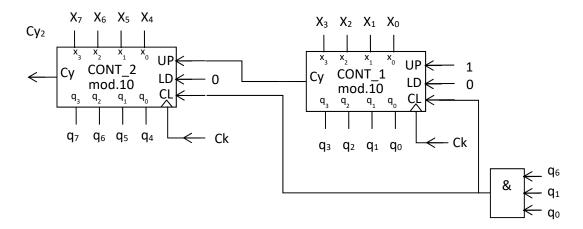

Problema 3. En la siguiente figura se muestra un circuito secuencial síncrono basado en dos contadores idénticos módulo\_10 con la siguiente tabla funcional a nivel RT.

| UP | LD | CL | CONT ←                     |

|----|----|----|----------------------------|

| 1  | 0  | 0  | $CONT \leftarrow CONT + 1$ |

| -  | 1  | 0  | CONT $\leftarrow X_{3-0}$  |

| -  | -  | 1  | $CONT \leftarrow 0$        |

| 0  | 0  | 0  | $CONT \leftarrow CONT$     |

- a) Analice el circuito e indique, justificando su respuesta, qué operación global realiza identificando estados de inicio y fin.

- b) Modifique el circuito anterior para conseguir que el conjunto realice la operación de cuenta de  $28_{(10} 48_{(10)}$ . Diseñe la salida de acarreo global,  $Cy_g$ , para este contador.

| <b>Examen Final</b>        | Convocatoria 1 | 5-febrero-2015 |

|----------------------------|----------------|----------------|

|                            |                |                |

| <u> Apellidos, Nombre:</u> |                |                |

Problema 1. Las 16 letras que más se usan en español son "E A O S R N I D L C T U M P B G" (en ese orden). Esas letras se codifican en binario natural desde el valor 0 para la "E" hacia delante, el 1 para la "A", etc. Diseñe el circuito óptimo que, ante la llegada de una letra, indique si se trata de una vocal o de una consonante.

El circuito óptimo debe realizarlo con un solo tipo de puertas.

**Nota:** Es imprescindible que defina claramente sus variables y sus valores lógicos.

Problema 2. Un circuito tiene como entradas cuatro números de n bits, A, B, C y D. Usando sólo subsistemas combinacionales no programables y puertas se desea diseñar un circuito que dé a su salida qué número (C o D) se encuentra más cerca del valor medio de A y B. Se recomienda seguir el siguiente esquema:

- a. Diseñe un circuito MEDIA que calcule la media de dos números F y G.

- b. Diseñe un circuito ABS que calcule el valor absoluto de la diferencia de dos números J y K.

- c. Diseñe un circuito MENOR que seleccione a su salida el menor de dos números M y N.

- d. Implemente el circuito propuesto usando los módulos anteriores.

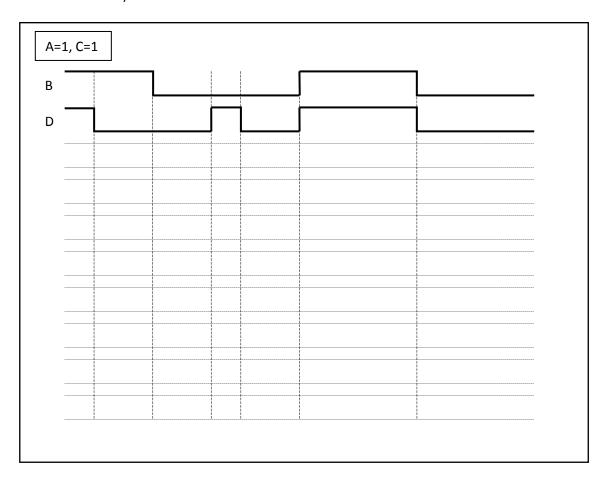

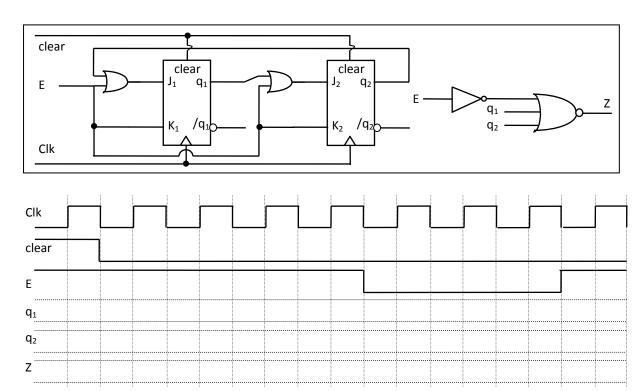

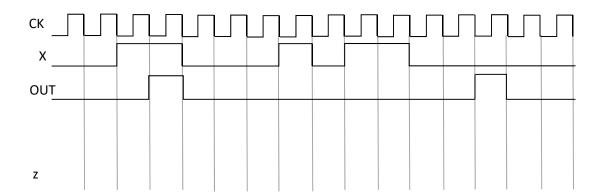

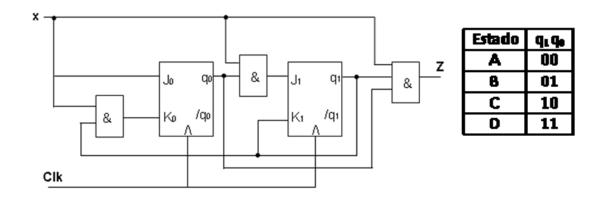

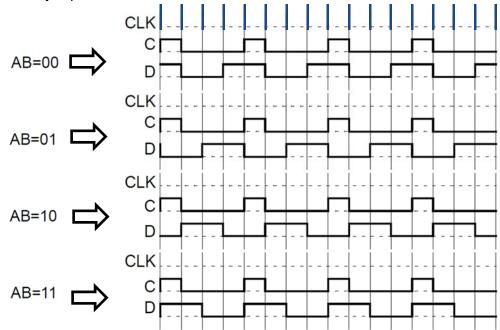

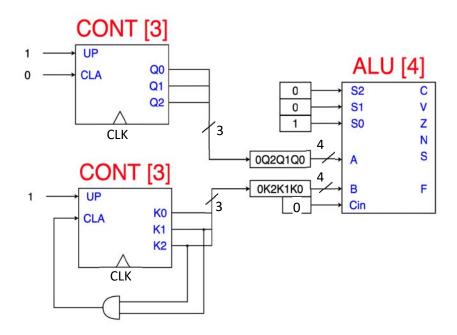

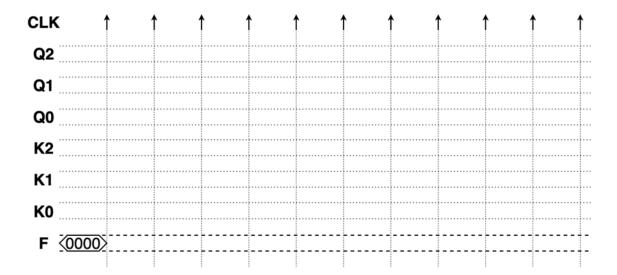

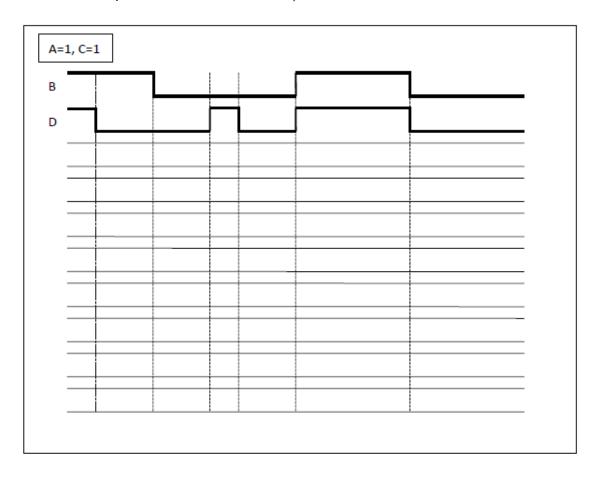

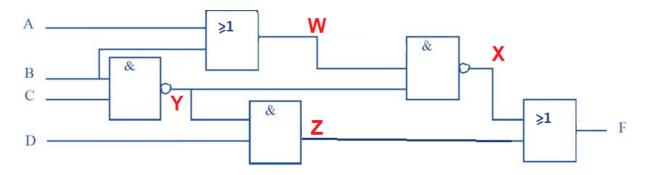

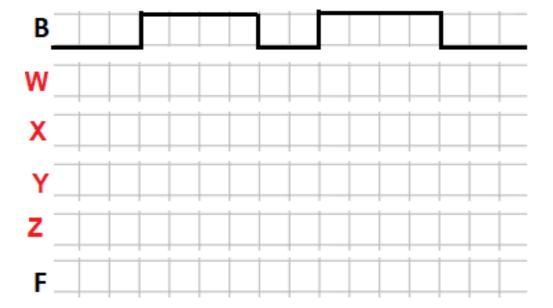

Problema 3. Analice el circuito de la figura, indicando las diferentes tablas que describen su operación síncrona.

Obtenga la evolución en el tiempo de las señales indicadas para las entradas que se muestran. (*Responda sobre el propio cronograma del enunciado*).

### Examen Final Convocatoria 2 4- septiembre -2015

| Apellidos, Nombre: |

|--------------------|

|--------------------|

Problema 1. Responda a cada una de las siguientes cuestiones:

- a. Para la representación de magnitudes en punto fijo con 10 bits en la parte entera y 4 bits en la parte fraccionaria:

- i. Indique en decimal el rango de valores representados: [menor-valor, mayor-valor].

- ii. Represente N = 38/5.

- iii. Calcule el error cometido en la representación de N anterior.

- b. Represente en hexadecimal:

- i. Código ASCII del carácter "signo más" (+)

- ii. Código ASCII con paridad par del carácter "signo más" (+)

- iii. Código ASCII con paridad impar del carácter "signo más" (+)

- c. Sean dos datos binarios de 8 bits, D1 = 0101 0101 y D2 = 1100 0011

- i. Indique si puede ser correcta o no lo es la afirmación: "D1 es un número con signo en Ca2". ¿Y la afirmación: "D2 es un número con signo en Ca2", puede ser o no correcta?

- ii. Indique, si es posible, el valor decimal de D1 y de D2.

- iii. Indique, si es posible, el valor decimal de E1=-D1 y de E2=-D2.

- d. Considere variables y funciones del álgebra de conmutación:

- i. De forma algebraica, demuestre la ley involutiva: x = (x')' donde  $x' \equiv NOT(x)$

- ii. Mediante tablas de verdad, demuestre si se cumple o no: "a·b = a·c"  $\Rightarrow$  "b=c"

- iii. Obtenga A⊕B⊕C como suma de productos y como producto de sumas.

Problema 2. Se desea diseñar un circuito electrónico que asista al conductor de un coche sobre la marcha más adecuada que debe utilizar en función de la velocidad del vehículo. El circuito conoce la velocidad por medio de una entrada binaria de 5 bits en la que se codifica, en binario natural, la cuarta parte del valor de la velocidad en kilómetros por hora. La relación entre velocidad y marcha recomendada se muestra en la tabla anexa.

Realice el diseño utilizando puertas lógicas.

| Rango de velocidades | Marcha     |

|----------------------|------------|

| 0 a 12 km/h          | 1ª         |

| 16 a 36 km/h         | 2 <u>ª</u> |

| 40 a 60 km/h         | 3 <u>a</u> |

| 64 a 88 km/h         | <b>4</b> ª |

| 92 km/h o más        | 5ª         |

Problema 3. En la figura se muestra la etapa típica de un diseño modular:

- a. Suponiendo que  $S_1S_0 = 00$ , dé la tabla de excitación y transición para el "biestable i" e identifique la operación que lleva a cabo para esa combinación de las variables de selección.

- b. Repita el apartado anterior para  $S_1S_0 = 01$ .

- c. Dibuje el subsistema resultante al conectar cuatro etapas.

- d. Describa funcionalmente el subsistema anterior dando la tabla a nivel RT.

| -   |    |    |     | 1   |

|-----|----|----|-----|-----|

| Exa | ım | Δn | H11 | กวเ |

|     |    |    |     |     |

Convocatoria 3

**03-diciembre -2015**

| Apellidos, Nombre:   |  |

|----------------------|--|

| Apelliuos, Nollible. |  |

Problema 1. Responda brevemente a cada una de las siguientes cuestiones:

a. Una palabra binaria tiene 10 Bytes. ¿Cuántos bits son? ¿Cuántos nibbles? Para la palabra binaria de 6 bits: 010011, indique el LSB y el MSB.

Nº bits=

Nº nibbles=

LSB =

MSB =

b. Dibuje un cronograma de una tensión que cambia entre -1 V y 3 V, tipo pulso con un duty cycle del 25% (duty cycle = T<sub>H</sub>/T %) y de 250 KHz. Los ejes deben incluir unidades y valores numéricos. Para la señal debe indicar la amplitud y el periodo.

Amplitud =

Periodo =

c. Represente el número  $59_{(10}$  en BCD y en Ca2 con 8 bits.

59<sub>(10</sub> en BCD: \_\_\_\_\_

59<sub>(10</sub> en Ca2:: \_\_\_\_\_

d. Simplifique paso a paso en el álgebra de Boole la expresión:

$F(a,b,c) = (ac')' \cdot (a+b') \cdot (a+b) =$

e. Se desea hacer OR(1,2,3,4,5,6,7), donde 1...7 son señales binarias de entrada, y se dispone de puertas OR-3 (OR de tres entradas). Dibuje el circuito. Repita si desea hacer NAND(1,2,3,4,5,6,7) y dispone de NAND-3. [Puede dibujar atrás.]

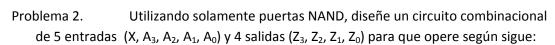

Problema 2. Utilizando solamente puertas NAND, diseñe un circuito combinacional de 5 entradas (X, A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub>, A<sub>0</sub>) y 4 salidas (Z<sub>3</sub>, Z<sub>2</sub>, Z<sub>1</sub>, Z<sub>0</sub>) para que opere según sigue:

$$X = 1$$

$\Rightarrow$   $Z_{3-0} = Ca1(A_{3-0})$

$$X = 0$$

$\Rightarrow$   $Z_{3-0} = Ca2(A_{3-0})$

- Problema 3. Se desea controlar las barreras de un paso a nivel (ver figura). A cierta distancia del paso a nivel, y sobre la vía, existen un par de sensores que se activan al pasar el tren (A y B). No se sabe si el tren es más largo o más corto que la distancia que separa a ambos sensores. Pero sí se sabe que los trenes siempre pasan en la dirección de A a B y que no pueden venir dos trenes consecutivos con una separación inferior a la distancia AB.

- a. Obtener el diagrama de estados de la máquina de Mealy que controla la señal P que actúa sobre las barreras. P=0 equivale a barrera bajada.

- b. Implementar dicha máquina usando biestables D y puertas NAND.

NOTA: Los sensores A y B actúan de manera que están activados mientras el tren esté pasando sobre ellos.

Examen Final Convocatoria 1 01-febrero-2016

Apellidos, Nombre:

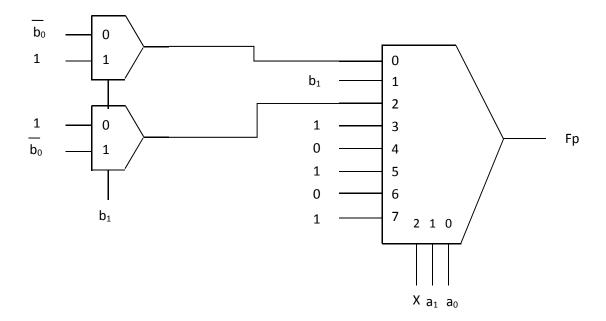

Problema 1. Sea  $F(a_1a_0b_1b_0)$  una función lógica que presenta el siguiente comportamiento:

Si X=0 y  $a_1a_0 \ge b_1b_0$ : F=0

$a_1a_0 < b_1b_0$ : F=1

Si X=1 y  $a_1a_0$  impar: F=0

$a_1a_0$  par: F=1

- 1. Diseñe el circuito óptimo en dos niveles para F usando únicamente puertas NAND's.

- 2. Si las variables de entrada están en único raíl modifique, si procede, el circuito anterior.

- 3. Para el circuito del apartado 2, muestre la onda de F si la entrada X cambia periódicamente entre 0 y 1, y el resto de las señales están fijas a los siguientes valores:

$a_1 a_0 = 00$  y  $b_1 b_0 = 10$ .

Considere que todas las puertas tienen retraso de valor unidad.

Problema 2. En el circuito siguiente, los módulos SUM son sumadores paralelos de dos números de 4 bits:

- 1. Obtenga la tabla de verdad de A=f (b<sub>3-0</sub>, C).

- 2. Analice el funcionamiento del mismo y rellene la tabla siguiente.

| X <sub>3-0</sub> | <b>y</b> <sub>3-0</sub> | Cı | b <sub>3-0</sub> | С | Α | Z <sub>3-0</sub> | C <sub>0</sub> |

|------------------|-------------------------|----|------------------|---|---|------------------|----------------|

| 0111             | 0010                    | 0  |                  |   |   |                  |                |

| 0111             | 0010                    | 1  |                  |   |   |                  |                |

| 0111             | 0011                    | 0  |                  |   |   |                  |                |

| 1001             | 1001                    | 1  |                  |   |   |                  |                |

3. Si  $x_{3-0}$ , e  $y_{3-0}$ , son números BCD, indique la función del circuito.

Problema 3. Analice los circuitos 1 y 2. Para cada caso, describa su funcionamiento mediante una tabla de operación e identifique el tipo de subsistema secuencial de que se trate.

**NOTA**: Observe que el Circuito 2 tiene un diseño 'modular'.

# Examen Final Convocatoria 2 05-septiembre-2016

| Anellidos        | , Nombre:   |  |  |

|------------------|-------------|--|--|

| <u>Apcillaos</u> | , NOTTIBLE. |  |  |

Problema 1. Responda a las siguientes cuestiones:

- a. Exprese en la notación IEEE-754 el valor de la suma P+Q donde P y Q son números con signo que están en la notación complemento a 2. Para ello, haga la suma convirtiendo previamente los números a decimal:

- P= \$23.1 (en notación complemento a 2, con 8 bits de parte entera).

- Q= \$AC.B (en notación complemento a 2, con 8 bits de parte entera).

- b. Considere la función (/x denota el complemento de x):

$$F(a,b,c,d) = (b+/c) \cdot /[a \cdot /(b \cdot {/c+d})]$$

- i. Obtenga, justificadamente, el mapa de Karnaugh de F.

- ii. Siendo  $G(a,b,c,d) = \Sigma(1,4,6,7,12,13) + \phi(5,15)$ , determine las funciones :

- 1. **F·G**

- 2. **F+G**

- 3. **F** ⊕ **G**

Nota: Las respuestas deben estar suficientemente explicadas.

Problema 2. Considere un comparador de 16 bits que, además de las entradas A[16] y B[16], dispone de una señal de control c que indica con c=0 que A y B son sin signo y, con c=1, que son con signo (Ca2). Las salidas son G, E y L.

- a. Describa formalmente este subsistema (estructura y función).

- b. Diseñe el comparador si dispone de los subsistemas habituales. Puede usar un comparador de magnitud de 16 bits.

- c. Indique los valores de todas las señales del circuito que ha diseñado en "b)" en los dos casos siguientes, si A=\$1005 y B=\$C999:

- 1. Para c=0.

- 2. Para c=1.

Problema 3. Se ha de realizar un detector de secuencia con **una entrada, X, y dos salidas Z1 y Z2**. La salida Z1 valdrá 1 cuando en X se detecte la secuencia 110 y la salida Z2 valdrá 1 cuando se detecte la secuencia 001. En otros casos serán cero. Se admite solapamiento.

- a. Obtenga el diagrama de estados correspondiente a una máquina de Mealy.

- b. Obtenga una implementación con biestables JK.

# Examen Final Convocatoria 3 02-diciembre -2016

| Apellidos, Nombre |  |

|-------------------|--|

| Apellidos, Nombre |  |

Problema 1. Considere el circuito de la figura.

- a. Analícelo a nivel lógico. Proporcione el mapa de Karnaugh de F(s, a, b, c, d).

- b. Rediseñe F(0,a,b,c,d) con el circuito mínimo utilizando solamente puertas NOR (puede usar también INV).

- c. Utilizando el circuito diseñado en el apartado anterior y un solo multiplexor del menor tamaño posible, obtenga el circuito que da F(s, a, b, c, d).

Problema 2. Se dispone de dos ALU de 4 bits idénticas a las estudiadas en teoría conectadas como se muestra en la figura.

Tras la operación efectuada con los datos A y B de 8 bits se observan los siguientes valores en las líneas de salida de cada una de ellas:

$$\begin{split} &C_{out2} = 0 & C_{out1} = 1 \\ &V_2 = 1 & V_1 = 1 \\ &Z_2 = 0 & Z_1 = 0 \\ &Signo_2 = 1 & Signo_1 = 0 \\ &F_{7-4} = 1 \ 0 \ 1 \ 0 & F_{3-0} = 0 \ 0 \ 1 \ 1 \end{split}$$

- a. Si A y B son magnitudes, ¿es el resultado F<sub>7-0</sub> correcto? Razone justificadamente la respuesta utilizando las salidas de las ALU.

- b. Proponga unos valores binarios para A y B que den los resultados de salida indicados anteriormente. Haga su comprobación en decimal.

Nota: Las respuestas deben estar suficientemente explicadas.

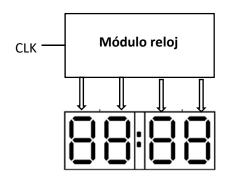

Problema 3. Se dispone de una señal de reloj CLK de 1/60 Hz. A partir de ella es posible obtener un reloj que muestre horas y minutos en visualizadores de 7 segmentos en el formato HH:MM donde HH es la hora actual (de 0 a 23) y MM es la indicación de los minutos (de 0 a 59).

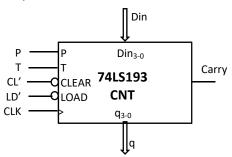

Se desea diseñar (ver figura) el módulo reloj que proporcione a la salida los cuatro dígitos BCD necesarios para realizar la visualización (es decir, dos para la hora, HH, y dos para los minutos, MM). Para ello se dispone de puertas NAND y cuatro integrados 74LS193, que es un contador síncrono de 4 bits, con señal de puesta a 0 asíncrona (CLEAR), carga en paralelo síncrona (LOAD), señales de inhibición (P y T) y salida de *carry* (CARRY).

| CL' | LD' | Р∙Т | CNT ←                  |         |

|-----|-----|-----|------------------------|---------|

| 0   | Х   | Х   | CNT ← 0                | (Asínc) |

| 1   | 0   | Х   | CNT ← Din              |         |

| 1   | 1   | 1   | $CNT \leftarrow CNT+1$ |         |

| 1   | 1   | 0   | $CNT \leftarrow CNT$   |         |

| Examen Final       | Convocatoria 1 | 27-enero-2017 |

|--------------------|----------------|---------------|

| Apellidos, Nombre: |                |               |

Problema 1. Responda a cada una de las siguientes preguntas teóricas:

- a. Defina qué es un bit. Escriba también sus valores y significado en los campos siguientes: conmutación (*switching*), electrónica y lógica. Explique, además, cuáles son los tamaños de las palabras habituales e identifique qué se entiende por MSB y LSB.

- b. Defina qué es el complemento a 2 de una magnitud M en el caso de n bits. Indique también cómo puede obtenerse a partir de la representación binaria de M y cómo se usa en la representación de números con signo en la notación Ca2.

- c. Explique qué es un MUX-2, descríbalo estructural y funcionalmente y escriba la ecuación algebraica de su salida.

- d. En una ALU como la realizada en teoría, explique para qué sirve Cout en la suma de magnitudes y para qué en la suma de números en Ca2.

- e. Una FSM de Mealy es una 5-tupla M(I, O, S,  $\lambda$ ,  $\delta$ ). Dibuje la forma general del Circuito Secuencial Síncrono (CSS) que la representa, identificando cada una de las partes del CSS con los símbolos de la 5-tupla.

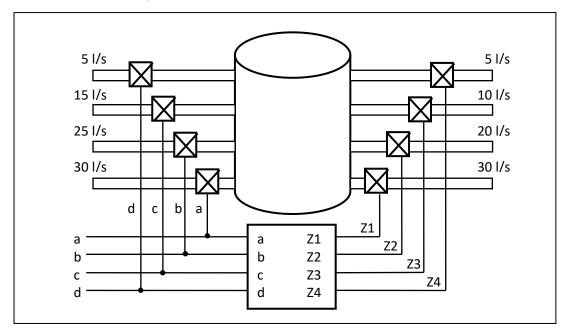

Problema 2. Al depósito de la figura acceden cuatro canalizaciones de líquido, cada una de las cuales es capaz de suministrar un caudal determinado. También posee cuatro canalizaciones de salida, pero que evacúan caudales diferentes. Cada una de las canalizaciones es controlada por una electroválvula cuyo estado (abierto o cerrado) depende de una variable binaria.

Sean a, b, c, d las variables binarias que controlan las electroválvulas de entrada y Z1, Z2, Z3, Z4, las de salida. Las variables de entrada son generadas externamente por un sistema de control del depósito, de forma que nunca estarán abiertas más de dos electroválvulas de entrada simultáneamente. Se desea que el depósito mantenga su contenido.

- a) Obtenga el mapa de Karnaugh que describe el comportamiento del circuito.

- b) Diseñe el circuito con puertas NAND.

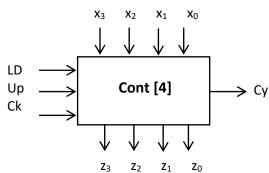

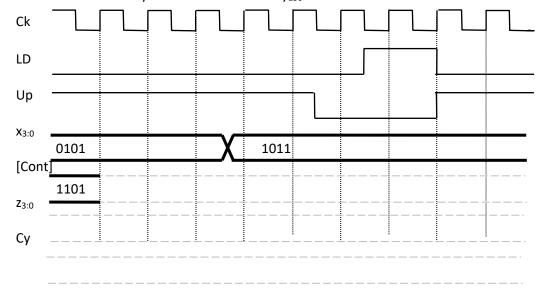

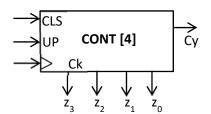

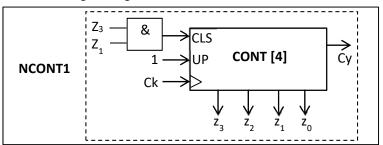

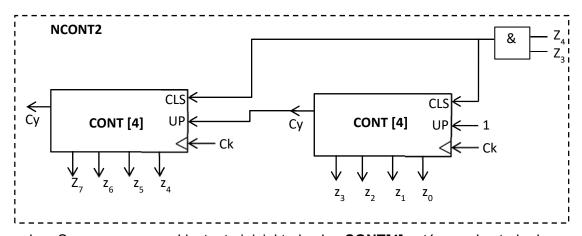

Problema 3. El circuito de la figura es un contador binario ascendente de 4 bits (mód. 16) que posee las operaciones síncronas de carga en paralelo (LD) y habilitación de cuenta (Up).

Además de las salidas de cuenta  $(z_3-z_0)$  posee una para indicar el fin de ciclo, Cy.

- a. Muestre su tabla de operación (descripción funcional).

- b. Complete el cronograma de la figura de abajo.

- Usando el menor número de contadores como el dado que necesite, obtenga un contador módulo

12. Inclúyale salida fin de ciclo Cy<sub>12</sub>.

- d. Usando el menor número de contadores (como el del enunciado) que necesite, obtenga un contador módulo 256. Inclúyale salida fin de ciclo Cy<sub>256</sub>.

#### Examen Final Convocatoria 2 04-septiembre-2017

| Anallidae Nam   | h    |  |  |

|-----------------|------|--|--|

| Apellidos, Nomi | ore: |  |  |

#### Problema 1. Responda las cuestiones siguientes:

- a. ¿Qué se entiende por representación posicional de magnitudes binarias de "n" bits? ¿Y por representación punto flotante IEEE-754 simple precisión?

- b. Siendo F una función lógica de 5 variables F(a,b,c,d,e), escriba un ejemplo de implicante de orden 1, I1, y otra de orden 3, I3. ¿Qué significa implicante prima esencial de una función? ¿Cómo se tratan las inespecificaciones de una función cuando se pretende encontrar la expresión mínima de ésta en suma de productos? ¿Y en producto de sumas?

- c. Para un convertidor de código Gray-Exceso 3 de 4 bits:

- i. Dé su tabla de verdad.

- ii. Exprese el bit LSB de salida como producto de maxtérminos.

- d. Para la ALU vista en teoría, indique qué resultados se obtienen en todas sus líneas de salida si los datos de entrada son A = \$AD y B=\$F6. Qué conclusiones se obtienen si:

- i. A y B son magnitudes

- ii. A y B son números con signo en notación complemento a 2.

- e. Para un contador mod- $2^k$  diseñado con biestables T, indique las ecuaciones de excitación de la etapa típica  $T_i$  para que realice la operación de cuenta arriba. ¿Y para la cuenta abajo? ¿Y para la carga en paralelo del dato  $X_{k-1}$ ...  $X_0$ ?

Problema 2. Antes de hacer la parte principal del problema (b) debe realizar la parte (a).

- a. Obtenga una expresión lógica para la función completamente especificada T(x, y) donde T=1 si se cumple la expresión "si x es cierto, entonces y es cierto" y T=0 en otro caso.

- b. Florencio¹ va a ir a una fiesta esta noche, pero no solo. Tiene cuatro nombres en su agenda: Ana, Bea, Carmen y Diana. Puede invitar a más de una chica pero no a las cuatro. Para no romper corazones, ha establecido las siguientes normas:

- Si invita a Bea, debe invitar también a Carmen.

- Si invita a Ana y a Carmen, deberá también invitar a Bea o a Diana.

- Si invita a Carmen o a Diana, o no invita a Ana, deberá invitar también a Bea.

Antes de llamarlas por teléfono, quiere utilizar un circuito que le indique cuándo una elección no es correcta.

Ayúdale diseñando ese circuito usando exclusivamente multiplexores de tipo MUX 4:1 y MUX 2:1.

Nota: La parte (a) supone el 20% de la nota y la (b), el 80%.

<sup>&</sup>lt;sup>1</sup> Si lo prefiere, sustituya Florencio por Fabiola; Ana por Alberto; Bea por Bernabé; Carmen por Carlos; y Diana por David. La cuestión es hacer el problema bien.

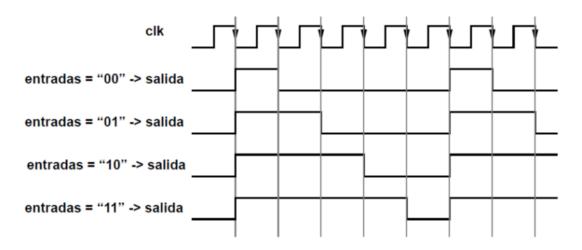

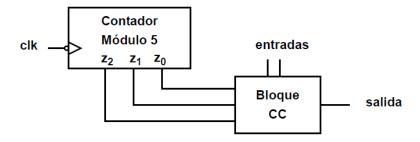

Problema 3. En muchos sistemas es útil el empleo de señales de ancho de pulso modulado. Estas señales se caracterizan porque, manteniendo una frecuencia fija, varía el porcentaje del tiempo que la señal está a '1'.

Se desea diseñar un circuito secuencial que, en función de una entrada de 2 bits, genere una señal de ancho de pulso modulado siguiendo el siguiente esquema de funcionamiento:

- a. Realice el diagrama y la tabla de estados de este circuito como máquina de Moore.

- b. Diseñe el circuito que realice dicho diagrama de estados empleando biestables D y puertas lógicas.

- c. La funcionalidad propuesta en el enunciado puede conseguirse, de una forma alternativa, mediante el empleo de un contador módulo 5 y un circuito combinacional según el esquema de abajo. Obtenga la tabla de verdad del bloque combinacional "CC". Explique y justifique convenientemente el contenido de dicha tabla de verdad.

**NOTA**: Obvie el problema que puede ocurrir si la señal de entrada cambia mientras se está generando la forma de onda.

Examen Final Convocatoria 3 29-Noviembre -2017

| re: |

|-----|

| re: |

Problema 1. Responda a cada una de las siguientes preguntas teóricas:

- a. Defina las relaciones que debe haber entre las tensiones de salida y las tensiones de entrada de una puerta lógica para tener un funcionamiento correcto. Describa además el concepto de margen de ruido y de fan-out.

- b. Analice la expresión

$$F(abc) = [(a \oplus b) c] \oplus b$$

hasta obtener una expresión sp mínima. Indique de qué subsistema combinacional se trata e identifique los distintos terminales.

- c. Indique cómo comparar dos números sin signo de 8 bits usando una ALU como la estudiada en teoría. Ídem para dos números con signo.

- d. Compare las máquinas de Moore y Mealy.

Problema 2. En una ALU de 6 bits similar a la diseñada en teoría se acaban de sumar dos números, A y B. El resultado S que muestra la ALU es "101 101", Cout= 0 y V = 0.

- a. Discuta este resultado en función del tipo de números de A y B (esto es, si son números sin o con signo).

- b. Repita lo anterior para los otros tres casos posibles de Cout y V (01, 10 y 11).

- c. Ponga, si es posible, cuatro ejemplos de valores binarios de A y B que siempre den el mismo S=101101 y que cada uno conduzca a uno de los 4 casos posibles de Cout y V.

- d. Para los ejemplos anteriores, obtenga los valores decimales equivalentes y compruebe si las sumas binarias han sido correctamente realizadas.

Notas: La respuesta debe estar suficientemente explicada. Sobre 10, las partes "a, b, c" valen 3, y la "d" vale 1

Problema 3. La siguiente secuencia de salida es generada por una máquina síncrona de tres estados en respuesta a la secuencia de entrada x:

Ciclo: 1 10 11 12 13 14 15 x: z:

- a. Obtenga razonadamente la tabla de estados de la máquina.

- b. Realice el circuito usando biestables JK y puertas.

| Examen Final       | Convocatoria 1 | 30-enero-2018 |

|--------------------|----------------|---------------|

| Apellidos, Nombre: |                |               |

Problema 1. Responda a cada una de las siguientes cuestiones:

a. Explique qué son las descripciones estructural y funcional.

Como ejercicio, aplíquelo a un circuito codificador de prioridad con las siguientes especificaciones:

Tiene 5 entradas: cuatro de datos activas en alta (X3:X0, siendo X3 la de mayor prioridad y X0 la de menor) y una de habilitación activa en baja (/ENI). Posee 4 salidas: dos (Z1Z0) que indican la dirección de la entrada activa de mayor prioridad y otras dos (/ENO y /GRS), ambas activas en baja, donde /ENO se activa cuando el codificador esté habilitado pero no tenga ninguna entrada X3:X0 activa y /GRS se activa cuando el codificador esté habilitado y tenga activa alguna entrada X3:X0.

- b. Explique y compare los sistemas de representación de números fraccionarios en punto fijo y en punto flotante.

- Como ejercicio, para el punto fijo considere palabras de 8 bits con dos de ellos dedicados a la parte fraccionaria. Indique el rango de representación para el caso de números con signo basados en el Ca2 y obtenga el valor decimal que tendría la palabra \$EA. Obtenga ese valor en el estándar de IEEE-754 de simple precisión (dé la respuesta en hexadecimal).

- c. Demuestre <u>algebraicamente</u> a partir de los postulados del álgebra de Boole las leyes de absorción. Después, demuestre <u>mediante tablas de verdad</u> la ley asociativa para la AND en el álgebra de conmutación.

Como ejercicio, simplifique la expresión  $F = (a' + a' \cdot b) \cdot [(a \cdot [b \cdot c'])' + b \cdot c']$

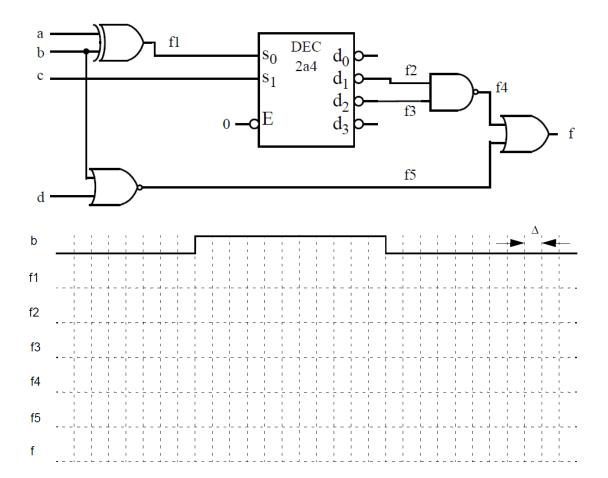

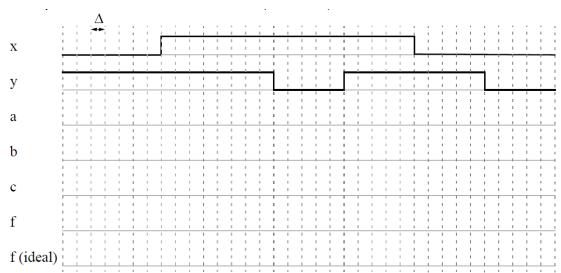

Problema 2. Analice el funcionamiento del circuito de la figura:

- a. Suponiendo el comportamiento ideal de todos los componentes, obtenga la expresión algebraica de la salida en forma de suma de productos.

- b. Suponiendo que todos los componentes tienen un retraso D, obtenga la evolución de la salida para el caso particular de que a = c = 1, d = 0 y b cambia.

- c. Realice un diseño alternativo optimizado de f usando sólo MUX4:1.

Problema 3. Diseñe un circuito de Moore que detecte la secuencia "0, 1, 0" (no hay grupos de bits) en una entrada X y que posea una señal de puesta a cero asíncrona, CLA. [La parte asíncrona de CLA **no** debe incluirse en los grafos de estado].

- a. Dé el grafo de estados si no se admite solapamiento.

- b. Dé el grafo de estados si se admite solapamiento. <u>Para este caso</u> haga también los apartados siguientes.

- c. Determine las secuencias de estado y de salida para las siguientes secuencias de entrada que se dan en la tabla. (Cada celda indica el valor presente en cada ciclo de reloj). Verifique si la secuencia obtenida detecta la secuencia deseada, explicando por qué.

- d. Obtenga el circuito con biestables JK y puertas.

| CLA | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| X:  | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| S:  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| z:  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

## Examen Final Convocatoria 2 03- septiembre -2018

| Apellidos, Nombre: |

|--------------------|

|--------------------|

Problema 1. Responda a las siguientes cuestiones:

- a. Obtenga el valor hexadecimal del código ASCII con paridad par de M así como del 51<sub>(10)</sub>.

- b. Realice un cronograma para la salida z siendo b=c=1 y  $a: 0 \rightarrow 1 \rightarrow 0 \rightarrow 1$  usando el modelo de retraso unidad para todas las puertas.

c. Analice y explique con palabras la operación que realiza el siguiente circuito. [El orden de las variables de salida es importante para interpretar la operación; use  $Z_1Z_0$ ].

- d. Cuando al sumar dos números con signo (A + B) se obtiene V = 1, ¿cómo o dónde se puede encontrar el valor correcto de la suma?

- e. Dispone de un registro **RID8** de desplazamiento a izquierda y a derecha de 8 bits. Descríbalo formalmente a nivel RT. Construya uno equivalente de 24 bits usando **RID8**s.

Problema 2. Se desean comparar dos magnitudes de 7 bits, M y N. Determine el circuito si:

- a. Dispone de un comparador de 8 bits como el dado en teoría (esto es, también tiene entradas "gel").

- Dé también la solución si usa un comparador de 8 bits sin entradas "gel".

- b. Dispone de comparadores de 4 bits como el dado en teoría (esto es, con entradas "gel").

- c. Dispone de comparadores de 4 bits sin entradas "gel".

- d. Se desea incorporar una señal HAB para habilitar la comparación de M y N. Dé la tabla funcional. Añada dicha señal (HAB) al circuito solución del caso "a" cuando usa comparador con "gel".

<u>Nota:</u> Si lo necesita, puede usar también puertas. El diseño debe tener el coste razonablemente más reducido.

Problema 3. Realice cada parte de forma independiente.

a. Un circuito secuencial dispone de dos entradas (A y B) por la que se reciben sendos números de 3 bits sin signo empezando por el LSB. Realice el diagrama de estados del autómata de Mealy que realiza la suma de dichos números y proporciona el resultado de 4 bits por la salida S. Entre número y número hay un bit que será ignorado a efectos de la suma. Se debe proporcionar cada bit de salida coincidiendo con los correspondientes bits de entrada.

Ejemplo:

b. Utilizando biestables JK y puertas lógicas, realice el diseño del siguiente diagrama de estados.

Nota: La entrada es P y tiene dos salidas que son x e y.

| Examen Final       | Convocatoria 3 | 03-aiciembre-2018 |

|--------------------|----------------|-------------------|

| Apellidos, Nombre: |                |                   |

Problema 1. Responda a cada una de las siguientes preguntas teóricas:

- a. Defina las relaciones que debe haber entre las tensiones de salida y las tensiones de entrada de una puerta lógica para tener un funcionamiento correcto. Describa además el concepto de margen de ruido y de fan-out.

- b. Analice la expresión  $\mathbf{f} = [(\mathbf{a} \oplus \mathbf{b}) \cdot \mathbf{c}] \oplus \mathbf{b}$  hasta obtener una expresión sp mínima. Indique de qué subsistema combinacional se trata e identifique los distintos terminales.

- c. Indique cómo comparar dos números sin signo de 8 bits usando una ALU como la estudiada en teoría. Ídem para dos números con signo.

- d. Compare las máquinas de Moore y Mealy.

Problema 2. Se dispone de un número con signo de 3 bits codificado en Signo-Magnitud cuando una entrada x es 0 y en Complemento a 2 si x es 1. **Manteniendo el código de entrada**, se desea transformarlo según las siguientes reglas:

- 1. Si el número es positivo, se le resta 2.

- 2. Si el número es negativo, se le suma 2.

- a) Obtenga las formas mínimas sp y ps.

- b) Obtenga el circuito óptimo correspondiente usando sólo un tipo de puertas.

- c) Indique cuál es el coste de la solución elegida así como en qué mejora a la otra solución.

**Nota:** Las respuestas deben estar suficientemente explicadas.

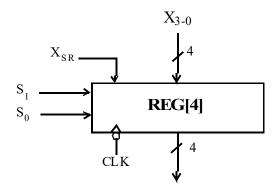

Problema 3. La figura representa la etapa típica de un subsistema secuencial de "n" bits. La etapa i=0 es especial y en ella las entradas de los canales 1 y 2 son ambas "1".

- 1. Describa el subsistema secuencial dando la descripción estructural y la tabla funcional, ésta a nivel RT. [Idea: Analice la etapa típica del circuito de la figura para poder inferir las funciones del subsistema.]

- 2. Suponiendo que n=8 y que inicialmente todos los biestables tienen almacenado un 0, escriba en hexadecimal la secuencia de contenidos del subsistema para la siguiente secuencia de entrada (el símbolo | señala el flanco activo de reloj:

$S_1 S_0: \hspace{1.5cm} 00 \hspace{.1cm} | \hspace{.1cm} 00 \hspace{.1cm} | \hspace{.1cm} 01 \hspace{.1cm} | \hspace{.1cm} 01 \hspace{.1cm} | \hspace{.1cm} 11 \hspace{.1cm} | \hspace{.1cm} 11 \hspace{.1cm} | \hspace{.1cm} 10 \hspace{.1cm} | \hspace{.1cm} 10 \hspace{.1cm} | \hspace{.1cm} 00 \hspace{.1cm} | \hspace{.1cm} 00 \hspace{.1cm} | \hspace{.1cm} | \hspace{.1cm} 00 \hspace{.1cm} | \hspace{.$

Solución (\$): 0

Examen Final Convocatoria 1 25-enero-2019

| Apellidos, Nombre: |

|--------------------|

|--------------------|

#### Problema 1. Responda a ambas cuestiones:

- a. Indique dos (2) **conceptos** importantes introducidos en cada uno de los temas siguientes. *Cada concepto debe ser explicado en 2 o 3 líneas.*

- i. Tema 3 Álgebra de conmutación

- ii. Tema 4 Análisis y diseño de circuitos combinacionales

- iii. Tema 5 Subsistemas combinacionales

- iv. Tema 7 Circuitos secuenciales síncronos

- v. Tema 8 Subsistemas secuenciales

- b. Sean V = \$CA y W = \$67:

- i. Ordénelos de mayor a menor si son magnitudes.

- ii. Ordénelos de mayor a menor si son números en Ca2.

- iii. Obtenga V+W si son números en Ca2 y:

- 1. dispone de un número de bits no limitado.

- 2. dispone de 8 bits únicamente.

- iv. Obtenga los opuestos (-V y -W) si son números en Ca2.

Problema 2. Se desea diseñar un circuito que asista al conductor de un coche sobre la marcha más adecuada que debe utilizar en función de la velocidad del vehículo. El circuito conoce la velocidad por medio de una entrada de 5 bits que codifican en binario natural la parte entera de la cuarta parte de la velocidad en km/h [entrada = parte entera (velocidad/4)]. La relación entre la velocidad y la marcha recomendada se muestra en la tabla anexa.

Realice el diseño usando únicamente puertas NOR.

| Rango de velocidades<br>(en km/h) | Marcha     |

|-----------------------------------|------------|

| 0 a 15                            | 1ª         |

| 16 a 39                           | 2 <u>ª</u> |

| 40 a 63                           | 3 <u>a</u> |

| 64 a 91                           | <b>4</b> ª |

| 92 o más                          | 5 <u>ª</u> |

Problema 3. Un circuito secuencial síncrono disparado por el flanco negativo de reloj posee la tabla de estados que se adjunta.

| 、X |      |      |       |

|----|------|------|-------|

| s  | 0    | 1    |       |

| A  | A, 0 | В, О |       |

| В  | C, 0 | В, 1 |       |

| С  | A, 0 | D, 0 | NS, z |

| D  | A, 0 | В, О |       |

- a) Realice el diagrama de estados del circuito.

- b) Compruebe si para la secuencia de entrada X que se da a continuación la secuencia de la señal OUT es o no solución para la salida z del circuito justificando la respuesta. En su caso, dé la onda de salida de z.

- c) Diseñe el circuito utilizando biestables T y puertas lógicas.

|              |                  | _                   |

|--------------|------------------|---------------------|

| Examen Final | Convocatoria 2   | 16-septiembre-2019  |

| Lainen finai | GUIIVULATUI IA Z | 10-26006111016-7013 |

| Apellidos, Nombre: |

|--------------------|

|--------------------|

Problema 1. Se dispone de una ALU como la estudiada en clase (2018/2019). Para números de 8 bits, si  $S_{2-0}$  = 001,  $C_{in}$  = 0, A=\$C5 y B es desconocido, en cada apartado, razone si pueden ocurrir los siguientes casos y exponga las conclusiones pertinentes:

- a. C=0, V=0, N=0, S=0 y Z=0.

- b. C= 1, V = 0, N = 0, S = 0 y Z = 0.

- c. C= 1, V = 1, N = 0, S = 1 y Z = 0.

- d. C= 0, V = 1, N = 1, S = 0 y Z = 0.

- e. C=0, V=0, N=1, S=1 y Z=1.

Problema 2. Las entradas C y D de 8 bits son números con signo en notación Ca2. Analice el circuito de la figura e indique verbalmente qué operación realiza.

.

Problema 3. Se desea diseñar un contador BCD descendente de un dígito. Debe tener carga paralela síncrona activa en alta, señal de inhibición de cuenta y salida de *borrow*. Dispone de contadores completos módulo 16 (con entrada de carga síncrona activa en alta, señal de inhibición de cuenta y salida de *borrow*), puertas lógicas y subsistemas combinacionales.

#### Examen Final Convocatoria 3 18-diciembre-2019

| Apellidos, Nombre: |

|--------------------|

|--------------------|

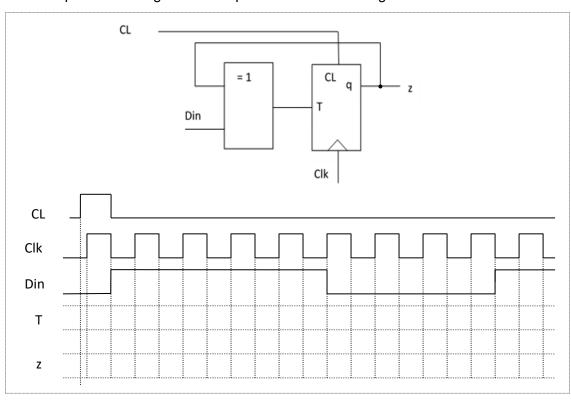

Problema 1. Responda a las siguientes cuestiones:

- a. Interprete la palabra binaria 10010011 como:

- Número en binario natural

- Número en Ca2

- Código ASCII con paridad impar

- BCD

- b. Describa la función que realiza un demultiplexor, sus entradas y salidas y su tabla de funcionamiento. Ponga un ejemplo de cómo construir un demultiplexor mayor con otros más pequeños.

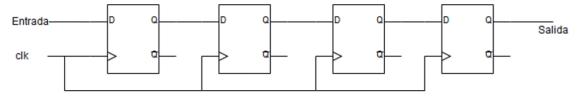

- c. ¿Qué subsistema es el siguiente circuito? Explique por qué.

Dibuje un pequeño cronograma para mostrar su funcionamiento, poniendo nombre y dibujando las señales intermedias.

Nombre: 18-dic-19

Problema 2. Considere la ALU de 8 bits desarrollada en teoría (ver Hoja Para Examen).

- a) Dado un número P con signo en Ca2 indique cómo obtener Ca2(P).

- b) Suponga que se conectan los siguientes valores a las entradas:  $A = $7E y B = $96 y S_2S_1S_0Cin = 0010$ . Indique los valores que aparecen en todas las salidas (incluidas las de estado). Interprete los resultados en los dos casos siguientes:

- 1) A y B son números sin signo

- 2) A y B son números con signo en Ca2.

- c) Repita el caso anterior si  $S_2S_1S_0Cin = 0101$  si:

- 1) A y B son números sin signo

- 2) A y B son números con signo en Ca2.

- d) Repita el caso anterior si  $S_2S_1S_0Cin = 1101$ .

Problema 3. En la siguiente figura se muestra un circuito secuencial síncrono basado en dos contadores idénticos módulo 10 con la siguiente tabla funcional a nivel RT.

| UP | LD | CL | CONT ←                     |

|----|----|----|----------------------------|

| 1  | 0  | 0  | $CONT \leftarrow CONT + 1$ |

| -  | 1  | 0  | CONT ← X <sub>3-0</sub>    |

| -  | -  | 1  | $CONT \leftarrow 0$        |

| 0  | 0  | 0  | CONT ← CONT                |

- a) Analice el circuito e indique, justificando su respuesta, qué operación global realiza identificando estados de inicio y fin.

- b) Modifique el circuito anterior para conseguir que el conjunto realice la operación de cuenta de  $28_{(10} 48_{(10)}$ . Diseñe la salida de acarreo global, Cyg, para este contador.

Convocatoria 1

23-enero-2020

|                                                                                        | Apellidos, Nombre:                                                                                                   |                                  |                |                         |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------------|--|

|                                                                                        |                                                                                                                      |                                  |                |                         |  |

|                                                                                        |                                                                                                                      |                                  |                |                         |  |

| Pr                                                                                     | oblema 1. Responda a las siguier                                                                                     | ntes preguntas (son              | independient   | tes).                   |  |

| a.                                                                                     | Dispone de 12 bits para contar ma                                                                                    | gnitudes. Indique <b>e</b>       | n hexadecima   | al el rango de los      |  |

|                                                                                        | números correspondientes a:                                                                                          |                                  | (Tema          | <mark>2</mark> )        |  |

|                                                                                        | 1. Primeros 256 números (¼ k)                                                                                        | Respuesta: [                     | ,              | ]                       |  |

|                                                                                        | 2. Últimos 256 números (¼ k)                                                                                         | Respuesta: [                     | ,              | ]                       |  |

|                                                                                        | 3. Primeros 512 números (½ k)                                                                                        | Respuesta: [                     | ,              | ]                       |  |

|                                                                                        | 4. Primeros 1024 números (1 k)                                                                                       | Respuesta: [                     | ,              | ]                       |  |

|                                                                                        | 5. Los 1024 números que ocupan la parte central del rango total.                                                     |                                  |                |                         |  |

|                                                                                        |                                                                                                                      | Respuesta: [                     | ,              | ]                       |  |

| b.                                                                                     | Sean dos magnitudes $M_{(10}$ = $M_2$ $M_1$ $M_0$ y $N_{(10}$ = $N_2$ $N_1$ $N_0$ en los que cada cifra está en BCD. |                                  |                |                         |  |

|                                                                                        | Dispone de comparadores de magnitud de 4 bits con entradas de propagación (referidas                                 |                                  |                |                         |  |

|                                                                                        | omo "G <sub>0</sub> E <sub>0</sub> L <sub>0</sub> " o como "g e l").                                                 |                                  | (Tema          | (Tema 5)                |  |

|                                                                                        | 1. Indique el circuito que permita comparar M y N.                                                                   |                                  |                |                         |  |

|                                                                                        | 2. Aplíquelo al caso $M_{(10}=813 \text{ y } N_{(1)}$                                                                | <sub>.0</sub> =832 dando el valo | or de todas la | s señales del circuito. |  |

| c.                                                                                     | La ALU diseñada en clase tiene tres operaciones de resta (A-B-1, A-B y A-1). Justifique                              |                                  |                |                         |  |

| funcionamiento, y dibuje y explique la parte de los circuitos afectados centrándose en |                                                                                                                      |                                  |                | los centrándose en los  |  |

dos casos siguientes:1. Para la salida F.

**Examen Final**

- 2. Para el bit C.

- d. Describa estructural y funcionalmente un flip-flop tipo T disparado por el flanco de subida y con entrada asíncrona de puesta a cero activa en baja. (Incluya las diferentes tablas que representan su operación). (Tema 7)

(Tema 6)

Problema 2. Se desea diseñar un circuito electrónico que determina la posición de los primeros 5 finalistas de un concurso en función de una votación. La votación es hecha por mensajes SMS que son recogidos por un sistema que mide el tanto por ciento de los votos de cada finalista. Este sistema proporciona, codificado en binario, la **parte entera de la cuarta parte del porcentaje** de votos. La relación entre votos obtenidos y la posición del finalista se muestra en la tabla anexa.

- a. Obtenga el mapa lógico que genere en binario natural la posición del concursante según la tabla.

- b. Diseñe el circuito óptimo en dos niveles que genera el MSB de la posición usando únicamente puertas NAND.

- c. Diseñe la salida LSB mediante un MUX-4.

Nota: Considere doble raíl.

| Porcentaje de Votos | Posición Lograda |

|---------------------|------------------|

| 96 o más            | 1 <sup>a</sup>   |

| 72-95               | 2ª               |

| 48-71               | 3ª               |

| 24-47               | 4 <sup>a</sup>   |

| 0-23                | 5ª               |

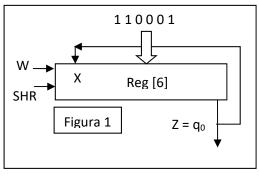

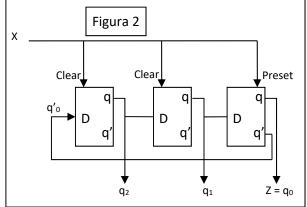

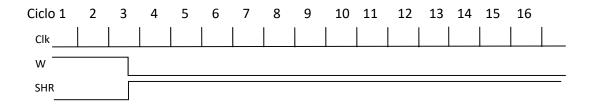

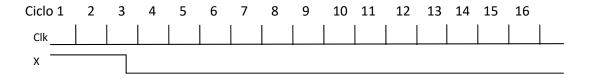

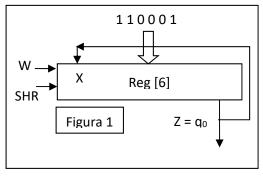

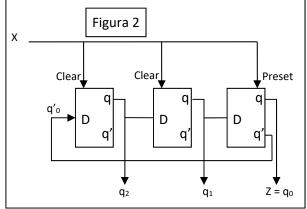

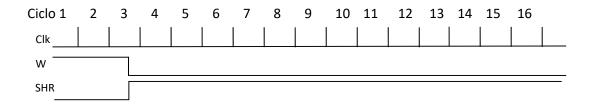

Problema 3. El circuito de la Figura 1 está formado por un registro "Reg" de 6 bits con carga en paralelo y desplazamiento a la derecha, de forma síncrona (reloj Clk no dibujado). El circuito de la Figura 2 muestra un circuito con biestables D síncronos (reloj Clk no dibujado), dos de ellos con Clear asíncrono y el otro con Set asíncrono.

a. Para la siguiente secuencia de excitación, obtenga el valor de Z de la Figura 1. Si lo desea, puede hacer una tabla con los ciclos de Clk numerados, en vez del diagrama de tiempos.

b. Para la siguiente secuencia de excitación, obtenga el valor de Z de la Figura 2. Si lo desea, puede hacer una tabla con los ciclos de Clk numerados, en vez del diagrama de tiempos.

c. Compare ambos circuitos funcionalmente y en coste.

Examen Final Recuperación Parte 2 23-enero-2020

Nombre: GRUPO: G1 G2 G3

Problema 1. Dispone de ALUs como la explicada en clase. Considere las magnitudes M= 7 y N = 8, así como los números con signo P = -7 y Q = +8. Indique: 1/cómo haría las siguientes operaciones (tiene que dar valores a **todas las entradas**), 2/realícelas (tiene que dar valores a **todas las salidas**) y 3/**discuta los resultados que obtenga**. Por último, 4/compruebe su respuesta haciendo la operación en decimal:

- a. R1 = M + N usando una sola ALU de 8 bits.

- b. R2 = P + Q usando una sola ALU de 8 bits.

- c. R3 = P Q usando una sola ALU de 8 bits.

- d. R4 = M N usando una sola ALU de 8 bits.

- e. R5 = P + Q usando dos ALU de 4 bits.

- f. R6 = P + Q usando una sola ALU de 4 bits.

Problema 2. El circuito de la Figura 1 está formado por un registro "Reg" de 6 bits con carga en paralelo y desplazamiento a la derecha, de forma síncrona (reloj Clk no dibujado). El circuito de la Figura 2 muestra un circuito con biestables D síncronos (reloj Clk no dibujado), dos de ellos con Clear asíncrono y el otro con Set asíncrono.

a. Para la siguiente secuencia de excitación, obtenga el valor de Z de la Figura 1. Si lo desea, puede hacer una tabla con los ciclos de Clk numerados, en vez del diagrama de tiempos.

b. Para la siguiente secuencia de excitación, obtenga el valor de Z de la Figura 2. Si lo desea, puede hacer una tabla con los ciclos de Clk numerados, en vez del diagrama de tiempos.

c. Compare ambos circuitos funcionalmente y en coste.

| <b>Examen Final</b> | Convocatoria 2 | 14- septiembre -2020 |

|---------------------|----------------|----------------------|

|                     |                |                      |

| Apellidos, Nombre:  |                |                      |

Problema 1. Circuitos aritméticos: dé una descripción detallada de los distintos circuitos aritméticos estudiados en clase. Esto es, para cada uno debe dar su definición, descripción estructural y funcional, ecuaciones de salidas y circuito. Los circuitos que debe contemplar son: HA, FA, sumador paralelo y sumador/restador (incorpore cuando sea necesario las salidas de estado de *carry* y de *overflow*).

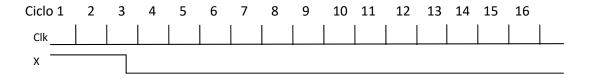

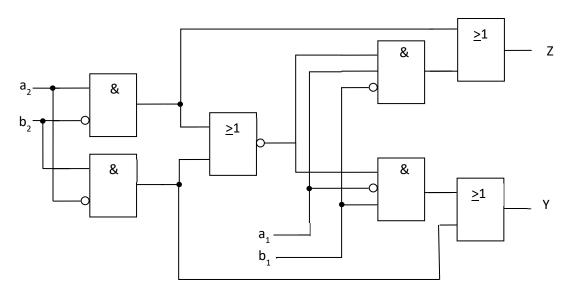

Problema 2. Se desea obtener una función lógica F con el siguiente comportamiento:

$a_1a_0$  par : F=1

Se ha propuesto como solución el circuito de la figura, con salida Fp, sin embargo, puede que no sea así.

a. Compruebe si hay errores indicando todos los que existan.

b. Corrija los errores del circuito de la figura para que Fp=F.

#### Problema 3. Los apartados a y b son independientes.

a. Por una entrada X se reciben secuencialmente números de 4 bits comenzando por LSB. Realice el diagrama de estados de una máquina de Mealy de un circuito que calcula el complemento a dos del número de entrada y lo muestra, vía serie, por su única salida Z. Por ejemplo:

**X**: 0000 1000 0110... **Z**: 0000 1111 0101...

b. Analice el circuito de la figura y obtenga el diagrama de estados. Suponga que el estado inicial es A.

Examen Final Convocatoria 3 16-diciembre-2020

| A    | pellidos | Nombre: |  |  |  |  |

|------|----------|---------|--|--|--|--|

| , ,, | JC111403 |         |  |  |  |  |

Problema 1. Considere la ALU de 8 bits desarrollada en teoría:

- a. Dado un número P de 8 bits con signo en Ca2, indique cómo obtener el Ca2(P).

- b. Indique cómo sumar dos números A y B de 8 bits y especifique también cómo detectar si el resultado es correcto para los siguientes casos:

- A y B son números sin signo

- A y B son números con signo en Ca2.

- c. Indique cómo comparar dos números A y B de 8 bits informando de si A>B, A=B o A<B:

- A y B son números sin signo

- A y B son números con signo en Ca2.

Nombre: 16-dic-2020

## Problema 2. Para el circuito de la figura:

- a. Analícelo.

- 1. Obtenga el mapa de Karnaugh

- 2. Interprete la funcionalidad del circuito considerando que las entradas representan a sendos datos de 2 bits cada uno  $A=a_2a_1$  y  $B=b_2b_1$ .

- b. Dibuje el cronograma de la salida Z del circuito de la figura si " $a_2$ " es una señal cuadrada de 10 Mhz de frecuencia, " $b_2 = b_1 = 0$  y  $a_1 = 1$ " y las puertas tienen un retraso de 10 ns.

Problema 3. En binario y punto fijo, la división por dos (A/2) consiste básicamente en un desplazamiento a la derecha. Obviamente, si A es un número con signo, el valor A/2 debe mantener el signo de A. Por otra parte, la división pierde un bit de precisión cuando A es impar. Suponga que dispone de registros universales de 8 bits (RU8).

- a. Describa formalmente a nivel RT su RU8. (Tiene que dar la descripción estructural y funcional de RU8 como subsistema).

- b. En una aplicación se manejarán números A de 32 bits. Utilizando como componentes registros RU8, construya un subsistema con una señal de entrada DIV que permita obtener A/2 cuando DIV esté activo mientras que conserve el dato en caso contrario.

- c. Si inicialmente el subsistema diseñado almacena el valor A[32] = 1010 1010 ... 1010, complete la siguiente secuencia con los sucesivos valores del subsistema:

DIV: 0 , 1 , 1 , 0 , 1 Subs: 1010...10 ,

<u>Notas</u>: Si su respuesta queda clara no es necesario que escriba los 32 bits de la secuencia, pudiendo poner puntos suspensivos en lo que claramente se repite. Además, puede poner la secuencia en columnas:

DIV=0 Subs: 1010 1010 ... 1010

DIV=1 Subs:

DIV=1 Subs:

DIV=0 Subs:

DIV=1 Subs:

|                 | men Final                                                                                         | Convocatoria                                                                                                                                                                                             | 1 19-febrero-2021                                                                                                                              |

|-----------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Apell</u>    | idos, Nombre:                                                                                     |                                                                                                                                                                                                          | <del>-</del>                                                                                                                                   |

|                 | <del>-</del>                                                                                      | las cuestiones siguientes. (S                                                                                                                                                                            | -                                                                                                                                              |

| a.              |                                                                                                   |                                                                                                                                                                                                          | BCD, en hexadecimal (\$) y en octal.                                                                                                           |

|                 |                                                                                                   | ario:<br>xadecimal:\$                                                                                                                                                                                    | BCD:octal:                                                                                                                                     |

| b.<br>c.<br>ejo | I. Indique si ca "D1 es un n "D2 es un n II. En el caso d D1 = ¿Qué es una implemplos de cada una | narios de 8 bits, D1 = 0101 ada afirmación puede ser co úmero con signo en Ca2": C úmero con signo en Ca2": C le que sea correcta, indique D2 =  icante? ¿Y una implicada ( de ellas para la función F(a | correcta o no:  Correcta Incorrecta  Correcta Incorrecta  su valor decimal:  (implicante de 0s)? Ponga dos  (bc) = $\Pi(1,2,4) \cdot d(0,7)$ . |

|                 |                                                                                                   |                                                                                                                                                                                                          |                                                                                                                                                |

|                 | Ejemplo1:                                                                                         |                                                                                                                                                                                                          | Ejemplo2:                                                                                                                                      |

|                 |                                                                                                   |                                                                                                                                                                                                          | Ejemplo2:                                                                                                                                      |