# ATmega48A/PA/88A/PA/168A/PA/328/P

# Instruction Set Summary

| Mnemonics      | Operands          | Description                              | Operation                             | Flags     | #Clocks |

|----------------|-------------------|------------------------------------------|---------------------------------------|-----------|---------|

| ARITHMETIC AND | LOGIC INSTRUCTION | s                                        |                                       |           |         |

| ADD            | Rd, Rr            | Add two Registers                        | $Rd \leftarrow Rd + Rr$               | Z,C,N,V,H | 1       |

| ADC            | Rd, Rr            | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$           | Z,C,N,V,H | 1       |

| ADIW           | Rdl,K             | Add Immediate to Word                    | Rdh:RdI ← Rdh:RdI + K                 | Z,C,N,V,S | 2       |

| SUB            | Rd, Rr            | Subtract two Registers                   | $Rd \leftarrow Rd - Rr$               | Z,C,N,V,H | 1       |

| SUBI           | Rd, K             | Subtract Constant from Register          | Rd ← Rd - K                           | Z,C,N,V,H | 1       |

| SBC            | Rd, Rr            | Subtract with Carry two Registers        | $Rd \leftarrow Rd - Rr - C$           | Z,C,N,V,H | 1       |

| SBCI           | Rd, K             | Subtract with Carry Constant from Reg.   | Rd ← Rd - K - C                       | Z,C,N,V,H | 1       |

| SBIW           | Rdl,K             | Subtract Immediate from Word             | Rdh:RdI ← Rdh:RdI - K                 | Z,C,N,V,S | 2       |

| AND            | Rd, Rr            | Logical AND Registers                    | Rd ← Rd • Rr                          | Z,N,V     | 1       |

| ANDI           | Rd, K             | Logical AND Register and Constant        | $Rd \leftarrow Rd \bullet K$          | Z,N,V     | 1       |

| OR             | Rd, Rr            | Logical OR Registers                     | $Rd \leftarrow Rd v Rr$               | Z,N,V     | 1       |

| ORI            | Rd, K             | Logical OR Register and Constant         | Rd ← Rd v K                           | Z,N,V     | 1       |

| EOR            | Rd, Rr            | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$          | Z,N,V     | 1       |

| COM            | Rd                | One's Complement                         | Rd ← 0xFF – Rd                        | Z,C,N,V   | 1       |

| NEG            | Rd                | Two's Complement                         | Rd ← 0x00 – Rd                        | Z,C,N,V,H | 1       |

| SBR            | Rd,K              | Set Bit(s) in Register                   | Rd ← Rd v K                           | Z,N,V     | 1       |

| CBR            | Rd,K              | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (0xFF - K)$ | Z,N,V     | 1       |

| INC            | Rd                | Increment                                | Rd ← Rd + 1                           | Z,N,V     | 1       |

| DEC            | Rd                | Decrement                                | Rd ← Rd – 1                           | Z,N,V     | 1       |

| TST            | Rd                | Test for Zero or Minus                   | $Rd \leftarrow Rd \bullet Rd$         | Z,N,V     | 1       |

| CLR            | Rd                | Clear Register                           | $Rd \leftarrow Rd \oplus Rd$          | Z,N,V     | 1       |

| SER            | Rd                | Set Register                             | Rd ← 0xFF                             | None      | 1       |

| MUL            | Rd, Rr            | Multiply Unsigned                        | $R1:R0 \leftarrow Rd \times Rr$       | Z,C       | 2       |

| MULS           | Rd, Rr            | Multiply Signed                          | R1:R0 ← Rd x Rr                       | Z,C       | 2       |

| MULSU          | Rd, Rr            | Multiply Signed with Unsigned            | R1:R0 ← Rd x Rr                       | Z,C       | 2       |

| FMUL           | Rd, Rr            | Fractional Multiply Unsigned             | R1:R0 ← (Rd x Rr) << 1                | Z,C       | 2       |

| FMULS          | Rd, Rr            | Fractional Multiply Signed               | R1:R0 ← (Rd x Rr) << 1                | Z,C       | 2       |

| FMULSU         | Rd, Rr            | Fractional Multiply Signed with Unsigned | R1:R0 ← (Rd x Rr) << 1                | Z,C       | 2       |

| BRANCH INST         |       |                                     |                                                      |            |       |

|---------------------|-------|-------------------------------------|------------------------------------------------------|------------|-------|

| RJMP                | k     | Relative Jump                       | $PC \leftarrow PC + k + 1$                           | None       | 2     |

| IJMP                |       | Indirect Jump to (Z)                | PC ← Z                                               | None       | 2     |

| JMP <sup>(1)</sup>  | k     | Direct Jump                         | PC ← k                                               | None       | 3     |

| RCALL               | k     | Relative Subroutine Call            | $PC \leftarrow PC + k + 1$                           | None       | 3     |

| ICALL               |       | Indirect Call to (Z)                | PC ← Z                                               | None       | 3     |

| CALL <sup>(1)</sup> | k     | Direct Subroutine Call              | PC ← k                                               | None       | 4     |

| RET                 |       | Subroutine Return                   | $PC \leftarrow STACK$                                | None       | 4     |

| RETI                |       | Interrupt Return                    | $PC \leftarrow STACK$                                | 1          | 4     |

| CPSE                | Rd,Rr | Compare, Skip if Equal              | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3             | None       | 1/2/3 |

| CP                  | Rd,Rr | Compare                             | Rd – Rr                                              | Z, N,V,C,H | 1     |

| CPC                 | Rd,Rr | Compare with Carry                  | Rd – Rr – C                                          | Z, N,V,C,H | 1     |

| CPI                 | Rd,K  | Compare Register with Immediate     | Rd – K                                               | Z, N,V,C,H | 1     |

| SBRC                | Rr, b | Skip if Bit in Register Cleared     | if (Rr(b)=0) PC ← PC + 2 or 3                        | None       | 1/2/3 |

| SBRS                | Rr, b | Skip if Bit in Register is Set      | if (Rr(b)=1) PC $\leftarrow$ PC + 2 or 3             | None       | 1/2/3 |

| SBIC                | P, b  | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC ← PC + 2 or 3                         | None       | 1/2/3 |

| SBIS                | P, b  | Skip if Bit in I/O Register is Set  | if (P(b)=1) PC ← PC + 2 or 3                         | None       | 1/2/3 |

| BRBS                | s, k  | Branch if Status Flag Set           | if (SREG(s) = 1) then PC←PC+k + 1                    | None       | 1/2   |

| BRBC                | s, k  | Branch if Status Flag Cleared       | if (SREG(s) = 0) then PC←PC+k + 1                    | None       | 1/2   |

| BREQ                | k     | Branch if Equal                     | if (Z = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRNE                | k     | Branch if Not Equal                 | if (Z = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRCS                | k     | Branch if Carry Set                 | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRCC                | k     | Branch if Carry Cleared             | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRSH                | k     | Branch if Same or Higher            | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRLO                | k     | Branch if Lower                     | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRMI                | k     | Branch if Minus                     | if (N = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRPL                | k     | Branch if Plus                      | if (N = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRGE                | k     | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1 | None       | 1/2   |

| BRLT                | k     | Branch if Less Than Zero, Signed    | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1 | None       | 1/2   |

| BRHS                | k     | Branch if Half Carry Flag Set       | if (H = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRHC                | k     | Branch if Half Carry Flag Cleared   | if (H = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRTS                | k     | Branch if T Flag Set                | if (T = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRTC                | k     | Branch if T Flag Cleared            | if $(T = 0)$ then PC $\leftarrow$ PC + k + 1         | None       | 1/2   |

| BRVS                | k     | Branch if Overflow Flag is Set      | if (V = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRVC                | k     | Branch if Overflow Flag is Cleared  | if (V = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2   |

| BRIE                | k     | Branch if Interrupt Enabled         | if ( I = 1) then PC ← PC + k + 1                     | None       | 1/2   |

| BRID                | k     | Branch if Interrupt Disabled        | if (I = 0) then PC ← PC + k + 1                      | None       | 1/2   |

# © 2020 Microchip Technology Inc.

| Mnemonics        | Operands     | Description                    | Operation                                                          | Flags   | #Clocks |

|------------------|--------------|--------------------------------|--------------------------------------------------------------------|---------|---------|

| BIT AND BIT-TEST | INSTRUCTIONS |                                |                                                                    |         | 1       |

| SBI              | P,b          | Set Bit in I/O Register        | I/O(P,b) ← 1                                                       | None    | 2       |

| CBI              | P,b          | Clear Bit in I/O Register      | I/O(P,b) ← 0                                                       | None    | 2       |

| LSL              | Rd           | Logical Shift Left             | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z,C,N,V | 1       |

| LSR              | Rd           | Logical Shift Right            | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z,C,N,V | 1       |

| ROL              | Rd           | Rotate Left Through Carry      | Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7)                                     | Z,C,N,V | 1       |

| ROR              | Rd           | Rotate Right Through Carry     | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z,C,N,V | 1       |

| ASR              | Rd           | Arithmetic Shift Right         | Rd(n) ← Rd(n+1), n=06                                              | Z,C,N,V | 1       |

| SWAP             | Rd           | Swap Nibbles                   | Rd(30)←Rd(74),Rd(74)←Rd(30)                                        | None    | 1       |

| BSET             | s            | Flag Set                       | $SREG(s) \leftarrow 1$                                             | SREG(s) | 1       |

| BCLR             | s            | Flag Clear                     | SREG(s) ← 0                                                        | SREG(s) | 1       |

| BST              | Rr, b        | Bit Store from Register to T   | $T \leftarrow Rr(b)$                                               | Т       | 1       |

| BLD              | Rd, b        | Bit load from T to Register    | Rd(b) ← T                                                          | None    | 1       |

| SEC              |              | Set Carry                      | C ← 1                                                              | С       | 1       |

| CLC              |              | Clear Carry                    | C ← 0                                                              | С       | 1       |

| SEN              |              | Set Negative Flag              | N ← 1                                                              | N       | 1       |

| CLN              |              | Clear Negative Flag            | N ← 0                                                              | N       | 1       |

| SEZ              |              | Set Zero Flag                  | Z ← 1                                                              | Z       | 1       |

| CLZ              |              | Clear Zero Flag                | Z ← 0                                                              | Z       | 1       |

| SEI              |              | Global Interrupt Enable        | ←1                                                                 | 1       | 1       |

| CLI              |              | Global Interrupt Disable       | ← 0                                                                | 1       | 1       |

| SES              |              | Set Signed Test Flag           | S ← 1                                                              | S       | 1       |

| CLS              |              | Clear Signed Test Flag         | S ← 0                                                              | S       | 1       |

| SEV              |              | Set Twos Complement Overflow.  | V ← 1                                                              | V       | 1       |

| CLV              |              | Clear Twos Complement Overflow | V ← 0                                                              | V       | 1       |

| SET              |              | Set T in SREG                  | T ← 1                                                              | т       | 1       |

| CLT              |              | Clear T in SREG                | T ← 0                                                              | т       | 1       |

| SEH              |              | Set Half Carry Flag in SREG    | H ← 1                                                              | н       | 1       |

| CLH              |              | Clear Half Carry Flag in SREG  | H ← 0                                                              | н       | 1       |

| DATA TRANS | FER INSTRUCTIONS |                                  |                                            |      |   |

|------------|------------------|----------------------------------|--------------------------------------------|------|---|

| MOV        | Rd, Rr           | Move Between Registers           | Rd ← Rr                                    | None | 1 |

| MOVW       | Rd, Rr           | Copy Register Word               | Rd+1:Rd ← Rr+1:Rr                          | None | 1 |

| LDI        | Rd, K            | Load Immediate                   | Rd ← K                                     | None | 1 |

| LD         | Rd, X            | Load Indirect                    | $Rd \leftarrow (X)$                        | None | 2 |

| LD         | Rd, X+           | Load Indirect and Post-Inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$    | None | 2 |

| LD         | Rd, - X          | Load Indirect and Pre-Dec.       | $X \leftarrow X - 1, Rd \leftarrow (X)$    | None | 2 |

| LD         | Rd, Y            | Load Indirect                    | $Rd \leftarrow (Y)$                        | None | 2 |

| LD         | Rd, Y+           | Load Indirect and Post-Inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$    | None | 2 |

| LD         | Rd, - Y          | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$    | None | 2 |

| LDD        | Rd,Y+q           | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                    | None | 2 |

| LD         | Rd, Z            | Load Indirect                    | $Rd \leftarrow (Z)$                        | None | 2 |

| LD         | Rd, Z+           | Load Indirect and Post-Inc.      | Rd ← (Z), Z ← Z+1                          | None | 2 |

| LD         | Rd, -Z           | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1$ , $Rd \leftarrow (Z)$ | None | 2 |

| LDD        | Rd, Z+q          | Load Indirect with Displacement  | Rd ← (Z + q)                               | None | 2 |

| LDS        | Rd, k            | Load Direct from SRAM            | Rd ← (k)                                   | None | 2 |

| ST         | X, Rr            | Store Indirect                   | (X) ← Rr                                   | None | 2 |

| ST         | X+, Rr           | Store Indirect and Post-Inc.     | (X) ← Rr, X ← X + 1                        | None | 2 |

| ST         | - X, Rr          | Store Indirect and Pre-Dec.      | $X \leftarrow X - 1, (X) \leftarrow Rr$    | None | 2 |

| ST         | Y, Rr            | Store Indirect                   | (Y) ← Rr                                   | None | 2 |

| ST         | Y+, Rr           | Store Indirect and Post-Inc.     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$    | None | 2 |

| ST         | - Y, Rr          | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$    | None | 2 |

| STD        | Y+q,Rr           | Store Indirect with Displacement | (Y + q) ← Rr                               | None | 2 |

| ST         | Z, Rr            | Store Indirect                   | (Z) ← Rr                                   | None | 2 |

| ST         | Z+, Rr           | Store Indirect and Post-Inc.     | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$    | None | 2 |

| ST         | -Z, Rr           | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$    | None | 2 |

| STD        | Z+q,Rr           | Store Indirect with Displacement | (Z + q) ← Rr                               | None | 2 |

| STS        | k, Rr            | Store Direct to SRAM             | (k) ← Rr                                   | None | 2 |

| LPM        |                  | Load Program Memory              | R0 ← (Z)                                   | None | 3 |

| LPM        | Rd, Z            | Load Program Memory              | $Rd \leftarrow (Z)$                        | None | 3 |

| LPM        | Rd, Z+           | Load Program Memory and Post-Inc | Rd ← (Z), Z ← Z+1                          | None | 3 |

| SPM        |                  | Store Program Memory             | (Z) ← R1:R0                                | None | - |

| IN         | Rd, P            | In Port                          | Rd ← P                                     | None | 1 |

| OUT        | P, Rr            | Out Port                         | P ← Rr                                     | None | 1 |

| PUSH       | Rr               | Push Register on Stack           | STACK ← Rr                                 | None | 2 |

| POP        | Rd               | Pop Register from Stack          | Rd ← STACK                                 | None | 2 |

| MCU CONTROL INSTRUCTIONS |  |                |                                          |      |     |  |  |  |

|--------------------------|--|----------------|------------------------------------------|------|-----|--|--|--|

| NOP                      |  | No Operation   |                                          | None | 1   |  |  |  |

| SLEEP                    |  | Sleep          | (see specific descr. for Sleep function) | None | 1   |  |  |  |

| WDR                      |  | Watchdog Reset | (see specific descr. for WDR/timer)      | None | 1   |  |  |  |

| BREAK                    |  | Break          | For On-chip Debug Only                   | None | N/A |  |  |  |

Note: 1. These instructions are only available in ATmega168PA and ATmega328P.

# PORTB – The Port B Data Register

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x05 (0x25)   | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

# DDRB – The Port B Data Direction Register

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| 0x04 (0x24)   | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# PINB – The Port B Input Pins Address<sup>(1)</sup>

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 0x03 (0x23)   | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R/W   |      |

| Initial Value | N/A   |      |

# TCCR1B – Timer/Counter1 Control Register B

| Bit           | 7        | 6     | 5 | 4     | 3     | 2    | 1    | 0    |        |

|---------------|----------|-------|---|-------|-------|------|------|------|--------|

| (0x81)        | /ICNC1// | ICESI |   | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W      | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  |        |

| Initial Value | 0        | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

## Bit 3 – WGM12: Waveform Generation Mode

Used together with WGM11:0 in TCCR1A and WGM13. When all the other bits are 0:

- WGM12=0: Normal mode. The counter counts the full range.

- WGM12=1: CTC mode. The counter is cleared when it matches the compare register (Clear Timer on Compare match).

| Table 16- | 5. Clock | Select Bit | Description                                             |

|-----------|----------|------------|---------------------------------------------------------|

| CS12      | CS11     | CS10       | Description                                             |

| 0         | 0        | 0          | No clock source (Timer/Counter stopped).                |

| 0         | 0        | 1          | clk <sub>I/O</sub> /1 (No prescaling)                   |

| 0         | 1        | 0          | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0         | 1        | 1          | clk <sub>I/O</sub> /64 (From prescaler)                 |

| 1         | 0        | 0          | clk <sub>I/O</sub> /256 (From prescaler)                |

| 1         | 0        | 1          | clk <sub>I/O</sub> /1024 (From prescaler)               |

| 1         | 1        | 0          | External clock source on T1 pin. Clock on falling edge. |

| 1         | 1        | 1          | External clock source on T1 pin. Clock on rising edge.  |

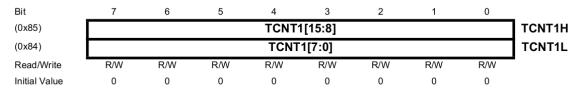

# TCNT1H and TCNT1L – Timer/Counter1

The two *Timer/Counter* I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See "Accessing 16-bit Registers" on page 122.

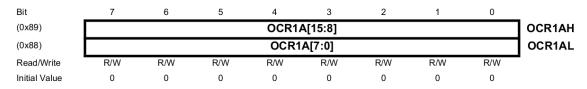

#### OCR1AH and OCR1AL – Output Compare Register 1 A

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

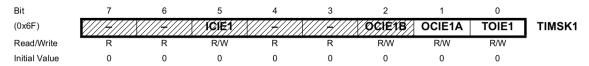

#### TIMSK1 – Timer/Counter1 Interrupt Mask Register

#### • Bit 1 – OCIE1A: Timer/Counter1, Output Compare A Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Output Compare A Match interrupt is enabled. The corresponding Interrupt Vector (see "Interrupts" on page 66) is executed when the OCF1A Flag, located in TIFR1, is set.

#### Bit 0 – TOIE1: Timer/Counter1, Overflow Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Overflow interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 66) is executed when the TOV1 Flag, located in TIFR1, is set.

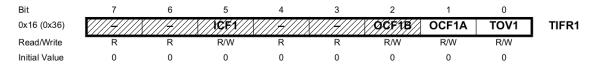

## TIFR1 – Timer/Counter1 Interrupt Flag Register

#### • Bit 1 – OCF1A: Timer/Counter1, Output Compare A Match Flag

This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register A (OCR1A).

OCF1A is automatically cleared when the Output Compare Match A Interrupt Vector is executed. Alternatively, OCF1A can be cleared by writing a logic one to its bit location.

## • Bit 0 – TOV1: Timer/Counter1, Overflow Flag

The setting of this flag is dependent of the WGM13:0 bits setting. In Normal and CTC modes, the TOV1 Flag is set when the timer overflows. Refer to Table 16-4 on page 141 for the TOV1 Flag behavior when using another WGM13:0 bit setting.

TOV1 is automatically cleared when the Timer/Counter1 Overflow Interrupt Vector is executed. Alternatively, TOV1 can be cleared by writing a logic one to its bit location.