# Capítulo 3

# Análisis y Diseño de Circuitos Combinacionales

# 3.1. Puertas y Familias Lógicas

# 3.1.1. Puertas Lógicas

Las funciones de conmutación estudiadas en el capítulo 2 pueden ser descritas por el conjunto de operadores AND, OR y NOT y variables de entrada. Estos operadores lógicos pueden implementarse físicamente mediante circuitos electrónicos que, en lugar de manejar valores lógicos como el 0 y el 1, utilizan niveles de tensión (voltaje) o corriente (intensidad). Los circuitos que implementan las operaciones lógicas básicas se denominan PUERTAS LÓGICAS.

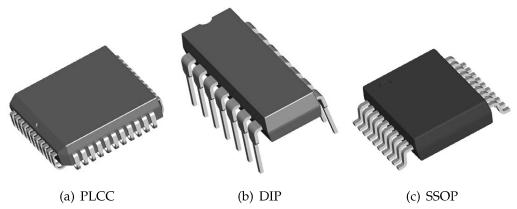

Las puertas lógicas contienen componentes electrónicos como transistores, diodos, etc. y estos se pueden encontrar de forma discreta (distinguibles a simple vista) o integrada en un sustrato de silicio que se ubica en el interior de un chip (circuito integrado o CI). La forma más habitual es la última ya que la primera ocupa gran espacio en comparación con el CI. Los circuitos integrados pueden tener diversos encapsulados: DIP, PLCC, SOJ, etc tal y como aparece en la figura 3.1. Además, los CI presentan otras ventajas:

- Bajo coste

- Bajo consumo

- Alta fiabilidad

- Alta velocidad de operación

- Reducido número de conexiones externas

Figura 3.1. Algunos de los encapsulados con los que se pueden presentar los circuitos integrados.

Se puede establecer una cladifiación de los CI atendiendo a la escala de integración, que representa una medida del número de componentes (según algunos autores) o de puerta lógicas (según otros) integrados en el mismo chip.

## Esta clasificación puede ser:

- SSI (Small Scale of Integration). Pequeña escala de integración. Comprende aquellos CI que contienen un número menor a 10 puertas lógicas o menos de 64 componentes.

- MSI (Medium Scale of Integration). Escala de integración mediana. Incluye aquellos CI que contienen un número de puertas inferior a 100 o un número de componentes menor a 2K.

- LSI (Large Scale of Integration). Gran escala de integración. Incluye aquellos CI que contienen un número de puertas inferior 10000 o ún número de componentes menor a 64K.

- VLSI (Very Large Scale of Integration). Escala de integración muy grande y comprende aquellos CI con un número menor de 100000 puertas o con menos de 2M componentes.

- ULSI (Ultra Large Scale of Integration). Escala de integración ultra grande. Aquí se incluyen todos los circuitos con un número mayor de 100000 puertas o más de 2M componentes.

# 3.1.2. Familias Lógicas

Una misma puerta lógica puede diseñarse internamente con componentes electrónicos diferentes provocando que las características eléctricas de un mismo operador lógico sean distintas. Así, por ejemplo, los valores de tensión e intensidad para las entradas y salida de una puerta AND fabricada con una tecnología pueden diferir de los de otra puerta AND que se haya fabricado con una tecnología diferente. No obstante, en ambos casos, la función lógica que implementa la puerta es la misma.

El conjunto de todos los componentes lógicos que han sido fabricados utilizando la misma tecnología se denomina FAMILIA LÓGICA. En la tabla 3.1 se muestran las principales familias lógicas agrupadas en dos grandes ramas: bipolar y MOS, que dan su nombre por el tipo de transitor que utilizan. Las familias más importantes son la CMOS y la TTL.

Tabla 3.1: Principales familias lógicas

| Bipolar | MOS  |

|---------|------|

| TTL     | pMOS |

| ECL     | nMOS |

| $I^2L$  | CMOS |

Cada familia, a su vez, se divide en una gran variedad de subfamilias o series lógicas. Por ejemplo, en la familia TTL se pueden encontrar las series: 74(TTL estándar), 74H (High Speed), 74L (Low Power), 74S (Schottky), 74LS (Low power Schottky), 74AS (Advanced Schottky), 74ALS (Advanced Low Power Schottky), 74F (Fast), etc.; y para la familia CMOS las series: 74HC (High Speed CMOS), 74HCT (High Speed CMOS, TTL compatible), 74AC (Advanced CMOS), 74ACT (Advanced CMOS, TTL compatible), 74FCT (Fast CMOS, TTL compatible), etc.

Dentro de cada serie se utiliza una numeración para identificar a un tipo de puerta lógica. Esta numeración se mantiene, incluso, para otras series lógicas. Por ejemplo, el C.I. 74LS00 contiene 4 puertas NAND, el C.I. 74LS04 contiene 6 puertas NOT, el C.I. 74LS08 contiene 4 puertas AND, todas ellas con tecnología TTL Low Schottky. Por su parte, el C.I. 74HC00 contiene 4 puertas NAND, el 74HC04 seis puertas NOT, ambas, con tecnología High Speed CMOS.

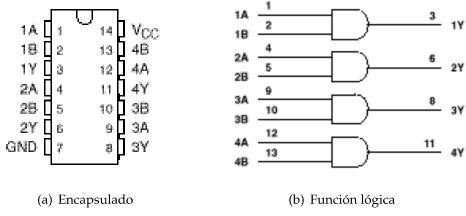

La figura 3.2 muestra el patillaje del circuito integrado 74AS08 y las funciones lógicas de las puertas que contiene. Puede observarse la existencia de terminales adicionales a los propios operadores, como son  $V_{cc}$  y GND, denominados alimentación y tierra respectivamente, y que suministran la tensión e intensidad necesarias para el funcionamiento del chip. El términal GND se conecta al nivel de tensión bajo (0 lógico), mientras que  $V_{cc}$  a 5V (3,3V) o nivel de tensión alto (1 lógico).

Figura 3.2. Descripción del circuito 74AS08.

La documentación técnica de una determinada puerta lógica incluye la tabla de verdad (function table) de la misma.

Como se puede observar en la figura 3.3, la tabla de función no contiene ni el valor lógico 0, ni el 1. El fabricante muestra los niveles de tensión de entrada y salida, H para el nivel alto, L para el nivel bajo y X para cualquier nivel de tensión (alto o bajo). Si las entradas A y B tienen un nivel alto de tensión, la salida genera un nivel alto de tensión; si la entrada A o la B tienen un nivel bajo de tensión, L, independientemente del nivel de tensión de la otra entrada, X, la salida mostrará un nivel bajo, L. Obsérvese que el comportamiento de la puerta se corresponde con el de una puerta AND, tan sólo se tienen que

| FUNCTION | N TABLE |

|----------|---------|

| (each)   | gate)   |

| INP | JTS | OUTPUT |  |  |  |  |

|-----|-----|--------|--|--|--|--|

| Α   | В   | Å      |  |  |  |  |

| Н   | Ι   | H      |  |  |  |  |

| L   | Х   | L      |  |  |  |  |

| Х   | L   | L      |  |  |  |  |

Figura 3.3. Tabla de función de cada puerta lógica del circuito 74AS08

sustituir los valores de tensión alto y bajo, por unos y ceros. Si se usa **lógica positiva**, el nivel de tensión alto representa al 1 lógico (H=1), y el nivel de tensión bajo, al 0 lógico (L=0). Si se usa **lógica negativa**, el nivel de tensión alto es el 0 lógico (H=0), y el nivel de tensión bajo, el 1 lógico (L=1)

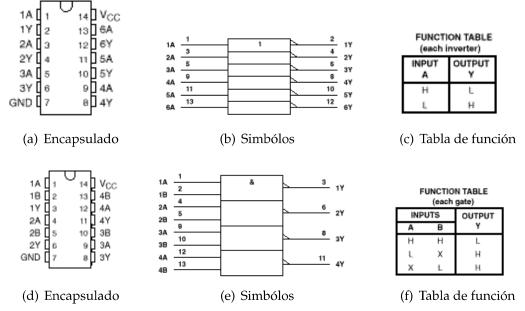

En la figura 3.4 se muestran diferentes circuitos junto con sus tablas de función.

Figura 3.4. Descripción del circuito 74AS04 (HEX NOT) y 74AS00 (QUAD NAND).

#### Características eléctricas de las puertas lógicas 3.1.3.

Los fabricantes de CI incorporan, en la documentación técnica de los chips, las especificaciones eléctricas y temporales de los mismos. En las tablas 3.2 y 3.3 se muestran partes de una hoja de datos de la puerta lógica comercial (74AS04) y de su versión militar (54AS04), que recogen algunos de los parámetros eléctricos más importantes para el diseño electrónico. A continuación se explicarán algunos de estos parámetros.

Tabla 3.2: Condiciones de trabajo recomendadas para el 74AS04

### recommended operating conditions

|                 |                                | S   | SN54AS04 |     |     | SN74AS04 |     |      |  |

|-----------------|--------------------------------|-----|----------|-----|-----|----------|-----|------|--|

|                 |                                | MIN | NOM      | MAX | MIN | NOM      | MAX | UNIT |  |

| Vcc             | Supply voltage                 | 4.5 | 5        | 5.5 | 4.5 | 5        | 5.5 | ٧    |  |

| VIH             | High-level input voltage       | 2   |          |     | 2   |          |     | ٧    |  |

| ٧ <sub>IL</sub> | Low-level input voltage        |     |          | 8.0 |     |          | 0.8 | ٧    |  |

| ЮН              | High-level output current      |     |          | -2  |     |          | -2  | mA   |  |

| loL             | Low-level output current       |     |          | 20  |     |          | 20  | mA   |  |

| TA              | Operating free-air temperature | -55 |          | 125 | 0   |          | 70  | °C   |  |

Tabla 3.3: Características eléctricas del 74AS04

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER | TEST O                                      | TEST CONDITIONS          |                    | N54AS0 | 4    | SI                 | N74AS0 | 4    | UNIT |

|-----------|---------------------------------------------|--------------------------|--------------------|--------|------|--------------------|--------|------|------|

| PARAMETER | lESI C                                      |                          |                    | TYP§   | MAX  | MIN                | TYP§   | MAX  | UNIT |

| ٧ıĸ       | $V_{CC} = 4.5 \text{ V},$                   | I <sub>I</sub> = -18 mA  |                    |        | -1.2 |                    |        | -1.2 | ٧    |

| VOH       | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$ | $I_{OH} = -2 \text{ mA}$ | V <sub>CC</sub> -2 | ?      |      | V <sub>CC</sub> -2 | !      |      | ٧    |

| VOL       | $V_{CC} = 4.5 V$ ,                          | I <sub>OL</sub> = 20 mA  |                    | 0.35   | 0.5  |                    | 0.35   | 0.5  | ٧    |

| in .      | $V_{CC} = 5.5 V$ ,                          | V <sub>I</sub> = 7 V     |                    |        | 0.1  |                    |        | 0.1  | mA   |

| IН        | $V_{CC} = 5.5 V$ ,                          | V <sub>I</sub> = 2.7 V   |                    |        | 20   |                    |        | 20   | μΑ   |

| III.      | $V_{CC} = 5.5 V$ ,                          | V <sub>I</sub> = 0.4 V   |                    |        | -0.5 |                    |        | -0.5 | mA   |

| lo¶       | $V_{CC} = 5.5 V$ ,                          | V <sub>O</sub> = 2.25 V  | -30                |        | -112 | -30                |        | -112 | mA   |

| lccн      | $V_{CC} = 5.5 V$ ,                          | V <sub>I</sub> = 0       |                    | 3      | 4.8  |                    | 3      | 4.8  | mA   |

| lCCL      | $V_{CC} \approx 5.5 \text{ V},$             | V <sub>I</sub> = 4.5 V   |                    | 14     | 26.3 |                    | 14     | 26.3 | mA   |

#### 3.1.3.1. Tensión o voltaje de alimentación

Se designa como  $V_{CC}$  (Supply voltage) y recoge los valores mínimo, máximo y nominal, referidos a tierra (GND), que se necesitan en el terminal  $V_{CC}$ para que el CI funcione. En la tabla 3.2 y para el integrado (74AS04), la tensión nominal de alimentación es de 5V, aunque el fabricante da un margen de valores que aseguran el buen funcionamiento del circuito ([4,5V,5,5V]). Fuera

<sup>§</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

del citado margen, el circuito puede no operar o, incluso, deteriorarse.

## 3.1.3.2. Función de transferencia

La representación del voltaje de salida de la puerta lógica frente al voltaje de entrada no suele ser suministrado por el fabricante, pero nos sirve para entender algunos parámetros eléctricos que sí aparecen en las tablas de características.

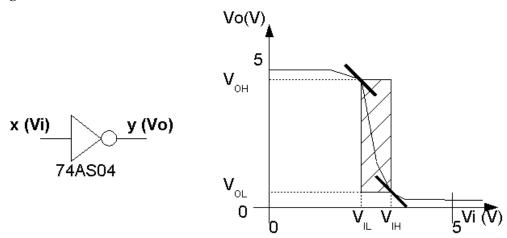

Si a una puerta de tipo inversor como el 74AS04, se conecta en su entrada un generador de tensión que pueda variar entre cero y cinco voltios y, en su salida, un medidor, la representación gráfica de los valores que da el medidor para cada tensión generada en su entrada, tendría la forma que se muestra en la figura 3.5.

Figura 3.5. Inversor y su función de transferencia.

Como se aprecia en la figura 3.5, para tensiones de entrada bajas (por ejemplo 0 V), la salida muestra un nivel alto de tensión ( $\approx 5V$ ); para tensiones más altas de entrada (p.e. 5V), la salida presenta un nivel bajo de tensión ( $\approx 0V$ )y para tensiones intermedias existe una región de transición. Salvo para la región de transición, el comportamiento de la puerta se corresponde con el de un inversor lógico, así, para un nivel bajo de tensión (0 lógico) en la entrada, la salida presenta un nivel alto de tensión (1 lógico) y si la entrada tiene un nivel alto (1 lógico), la salida presenta un nivel bajo (0 lógico). No se deben restringir los valores de tensión asociados al cero y uno lógicos a cantidades concretas, sino, más bien, a intervalos de valores para los que el modo de operación del CI se corresponda con el del operador lógico que implementa. Por

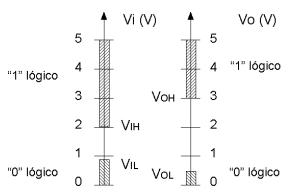

lo que muestra la figura 3.5 los límites de esos intervalos se establecen a partir de los puntos de la curva de transferencia  $V_o - V_i$  que tiene pendiente -1. Las coordenadas de estos puntos definen los siguientes parámetros:

- $V_{IH}$  Es la mínima tensión de entrada que se considera como un 1 lógico.

- $V_{IL}$  Es la máxima tensión de entrada que se considera como un 0 lógico.

- $V_{OH}$  Es la mínima tensión de salida que se considera como un 1 lógico.

- $V_{OL}$  Es la máxima tensión de salida que se considera como un 0 lógico.

Cualquier tensión de entrada comprendida en el rango  $V_i \in [0, V_{IL}]$  es un 0 lógico y genera una tensión de salida comprendida en el rango  $V_o \in [V_{OH}, V_{CC}]$  que se considera un 1 lógico.

Cualquier tensión de entrada comprendida en el rango  $V_i \in [V_{IH}, V_{CC}]$  es un 1 lógico y genera una tensión de salida comprendida en el rango de  $V_o \in [0, V_{OL}]$  que se considera un 0 lógico.

Por último, cualquier tensión de entrada comprendida entre  $V_i \in [V_{IL}, V_{IH}]$  genera una tensión de salida comprendida entre  $V_o \in [V_{OH}, V_{OL},]$  al que no se le asocia ningún valor lógico (zona de transición).

Para el CI 74AS04, cuyas hojas de características aparecen en la tabla 3.3, los valores tipicos de estos parámetros son:  $V_{IL}=0.8V$ ,  $V_{IH}=2V$ ,  $V_{OH}=3V$  para  $V_{CC}=5V$  y  $V_{OL}=0.35V$  (valor típico). Se destaca el hecho de que los niveles de tensión para los valores lógicos del 0 y del 1 varía de la entrada a la salida. En la figura 3.6 se han dibujado esos rangos.

En la tabla 3.4 se muestra como varían estos parámetros de una serie a otra. Tabla 3.4: Parámetros  $V_{IH}$ ,  $V_{IL}$ ,  $V_{OH}$  y  $V_{OL}$  de varias series lógicas.

|          | 74   | 74LS | 74ALS | 74F  | 74HC  | 74HCT | 74AC  |

|----------|------|------|-------|------|-------|-------|-------|

| $V_{IH}$ | 1,8V | 2,2V | 2,2V  | 2V   | 3,15V | 2V    | 3,25V |

| $V_{IL}$ | 0,6V | 0,8V | 0,9V  | 0,8V | 1,35V | 0,8V  | 1,65V |

| $V_{OH}$ | 2,2V | 2,9V | 2,9V  | 2,7V | 3,98V | 3,98V | 3,94V |

| $V_{OL}$ | 0,2V | 0,5V | 0,6V  | 0,5V | 0,26V | 0,26V | 0,36V |

Figura 3.6. Intervalos de tensiones asignadas para un cero y uno lógicos en entrada y salida del inversor 74AS04.

# 3.1.3.3. Margénes de ruido

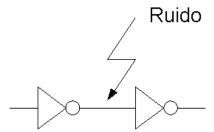

En la sección anterior nos encontramos con que los rangos para los unos y ceros lógicos varían dependiendo de si estos son de entrada o salida. Además, para la salida, dichos rangos son más restrictivos que para la entrada. Esta característica no es una casualidad sino una necesidad. En la figura 3.7 se han representado dos inversores conectados en serie (la salida del primer inversor con la entrada del segundo) mediante un cable que es susceptible de recibir voltajes inducidos externos (ruido) que se suman al nivel de tensión que genera el primer inversor. Es deseable que el conjunto de los dos inversores trabaje adecuadamente, a pesar de la existencia de ruido externo, siempre que éste se mantenga por debajo de un cierto nivel.

Figura 3.7. Dos inversores en cascada cuya interconexión está sometida a ruido externo.

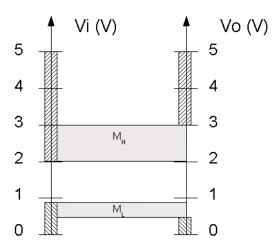

Si el primer inversor genera un 0 lógico como una tensión dada por  $V_{OL}$  y a ésta, se le suma cierto voltaje de ruido,  $V_N$ , para que el segundo inversor interprete adecuadamente la entrada como un 0 lógico, su  $V_{IL}$  debe ser lo suficientemente grande como para que  $V_{OL} + V_N \leq V_{IL}$ . Igualmente, si el primer inversor genera un 1 lógico como una tensión dada por  $V_{OH}$ , a la que se le suma el ruido,  $V_N$ , el receptor debe interpretar correctamente el 1 lógico si  $V_{IH} \leq V_{OH} - V_N$

Figura 3.8. Márgenes de ruido.

El margen de ruido representa la máxima amplitud de ruido medida en voltios, bajo la cual una puerta lógica puede funcionar correctamente. Existe un margen para el nivel alto,  $M_H$ , o margen de ruido superior y otro para el nivel bajo,  $M_L$  o margen de ruido inferior.

- $M_H = V_{OH} V_{IH}$ . Representa la máxima tensión de ruido admisible que no alteraría la interpretación de un uno lógico en la entrada de una puerta lógica.

- $M_L = V_{IL} V_{OL}$ . Representa la máxima tensión de ruido admisible que no alteraría la interpretación de un cero lógico en la entrada de una puerta lógica.

El márgen de ruido, M, de una serie lógica se define como el menor valor entre  $M_H$  y  $M_L$ . Para el circuito integrado 74AS04,  $M_H=1V$  y  $M_L=0.45V$ , por consiguiente, su márgen de ruido es de M=0.45V. En la tabla 3.5 se han representado los márgenes de ruido de algunas familias lógicas. Obsérvese que los circuitos CMOS son los que mayor margen de ruido disponen.

Tabla 3.5: Márgenes de ruido de algunas series lógicas.

|   | 74   | 74LS | 74ALS | 74F  | 74HC | 74HCT | 74AC  |

|---|------|------|-------|------|------|-------|-------|

| M | 0,4V | 0,3V | 0,3V  | 0,3V | 0,83 | 0,54V | 0,29V |

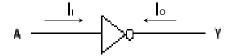

## 3.1.3.4. Corrientes de entrada y salida

Los terminales o pines de los circuitos integrados presentan intensidades (corrientes) que a su vez pueden ser de entrada hacia el interior del circuito (en cuyo caso se consideran positivas) o de salida hacia el exterior del mismo (corrientes negativas).

Figura 3.9. Intensidades de entrada y salida de un inversor.

El diseñador electrónico debe tener en cuenta las intensidades de entrada y salida de cada puerta lógica a la hora de interconectarla con otras puertas o con componentes analógicos como LEDS, resistencias, etc. Los fabricantes de suelen suministrar los siguientes parámetros:

- $I_{IH(max)}$  = Es la máxima intensidad que circula por la entrada de la puerta lógica cuando esta tiene un uno lógico.

- $I_{IL(max)}$  = Es la máxima intensidad que circula por la entrada de la puerta lógica cuando esta tiene un cero lógico.

- $I_{OH(max)}$  = Es la máxima intensidad que circula por la salida de la puerta lógica cuando esta tiene un uno lógico.

- $I_{OL(max)}$  = Es la máxima intensidad que circula por la salida de la puerta lógica cuando esta tiene un cero lógico.

La tabla 3.6 recoge los parámetros de intensidad de algunas de las familias lógicas más importantes. Obsérvese que los dispositivos con tecnología CMOS presentan menores intensidades que los de tecnología TTL.

## 3.1.3.5. Abanico de salida Fan-out

El fan-out define el número máximo de puertas lógicas que pueden conectarse a una puerta dada y se expresa en U.L. (unidades lógicas).

|          | 74        | 74LS      | 74ALS     | 74F       | 74HC       | 74HCT  | 74AC          |

|----------|-----------|-----------|-----------|-----------|------------|--------|---------------|

| $I_{IH}$ | $40\mu A$ | $20\mu A$ | $20\mu A$ | $20\mu A$ | $0.1\mu A$ | 0,1μΑ  | $0.1\mu A$    |

| $I_{IL}$ | -1,6mA    | -0,360mA  | -0,2mA    | -0,6mA    | -0,1mA     | -0,1mA | -0,1mA        |

| $I_{OH}$ | -0,4mA    | -0,4mA    | -0,4mA    | -1mA      | -4mA       | -4mA   | <i>-</i> 24mA |

| $I_{OL}$ | 16mA      | 8mA       | 8mA       | 20mA      | 4mA        | 4mA    | 24mA          |

Tabla 3.6: Tabla con los parámetros  $I_{IH(max)}$ ,  $I_{IL(max)}$ ,  $I_{OH(max)}$  e  $I_{OL(max)}$  de algunas series lógicas.

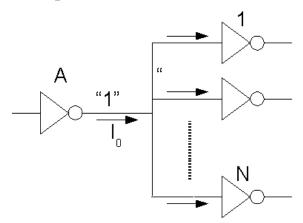

Supóngase que, a la salida de un inversor del tipo 74AS04, se conectan un número N de inversores del mismo tipo. Supóngase, también, que la salida del primer inversor (A) es un uno lógico, tal como muestra en la figura 3.10, donde, además, se han representado los sentidos reales de corriente.

Figura 3.10. Conjunto de N inversores conectados a uno dado que genera un 1 lógico en su salida.

Cuando la puerta A genera un uno lógico en su salida, la intensidad máxima que ésta puede suministrar (por ser negativa) es de  $I_{OH}=-2mA$ . Por otro lado, los inversores numerados desde el 1 hasta el N, si tienen un uno lógico en sus entradas, reciben, cada uno, una intensidad hacia el interior igual a  $I_{IH}=20\mu A$ . Por tanto, el número máximo, N, de puertas que se pueden conectar a una dad que genera un 1 lógico en su salida sería de:  $N\times I_{IH}=I_{OH}$ . Para el 74AS04, N=100.

La figura 3.11 muestra los sentidos de las corrientes para el supuesto en el que el inversor A genera un cero lógico en su salida. La intensidad máxima que la puerta A es capaz de absorber es de  $I_{OL}=20mA$ . Las puertas 1,2, ..N, que tienen un cero lógico en sus entradas son capaces de suministrar un máximo de  $N \times I_{IL} = N \times 0,5mA$ . Por tanto, el número máximo de inversores que pueden conectarse en esta situación al 74ASO4 es de N=20mA/0,5mA=

40.

Figura 3.11. Conjunto de N inversores conectados a uno dado que genera un 0 lógico en su salida.

El fan-out es valor más restrictivo de N para los dos supuestos anteriores y que, para la familia 74AS, es de 40 U.L. En la tabla 3.7 se muestran los fan-outs de algunas series lógicas.

Tabla 3.7: Fan-out de algunas series lógicas.

| 74    | 74LS  | 74ALS | 74F   | 74HC  | 74HCT | 74AC  |

|-------|-------|-------|-------|-------|-------|-------|

| 10 UL | 20 UL | 20 UL | 33 UL | 40 UL | 40 UL | 24 UL |

## 3.1.3.6. Disipación de potencia

Es la potencia disipada por el circuito integrado y se mide, normalmente, en mW. Un parámetro asociado es la intensidad  $I_{cc}$  o corriente que pasa a través del pin de alimentación  $V_{cc}$ . Al igual que las intensidades que circulan por los terminales de las puertas lógicas cambian en función de los niveles lógicos de estos, la intensidad que se suministra por el terminal  $V_{cc}$  también lo hace. El fabricante muestra dos valores de  $I_{cc}$ :  $I_{cch}$  e  $I_{ccl}$ , que se corresponden con las intensidades cuando las salidas del circuito integrado están a uno lógico y a cero lógico respectivamente. Tomando el valor medio de  $I_{cch}$  e  $I_{ccl}$  se puede obtener una buena aproximación del consumo real del integrado.

$$Potencia = V_{cc} \frac{I_{cch} + I_{cch}}{2}$$

# 3.1.4. Características temporales

Algunos parámetros de gran importancia que miden la **capacidad de res- puesta** de los circuitos integrados digitales son los tiempos de propagación o tiempos de retraso.

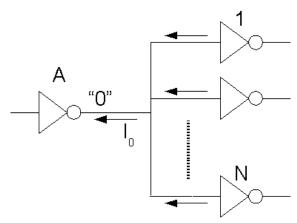

Figura 3.12. Tiempos de subida y bajada

- $t_{LH}$  = Es el tiempo que tarda la salida de la puerta en pasar desde un nivel bajo de tensión a un nivel alto (tiempo de subida).

- $t_{HL}$  = Es el tiempo que tarda la salida de la puerta en pasar desde un nivel alto de tensión a un nivel bajo (tiempo de bajada).

Los tiempos  $t_{LH}$  y  $t_{HL}$  se miden desde 10 % al 90 % de la señal de salida.

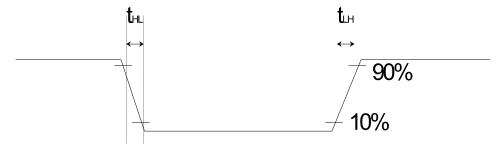

Aparte de los tiempos de subida y bajada, que definen la duración de la transición en la respuesta de la puerta, se tiene el tiempo de retardo, $t_p$  que mide cuánto tardaría una transición en la entrada de una puerta en reflejarse en su salida. Existen dos modalidades:

Figura 3.13. Tiempos de propagación

•  $t_{p_{LH}}$  = Mide el tiempo transcurrido desde que se produce una transición en la entrada de la puerta, y la salida de la misma comienza a sufrir una transición desde el nivel bajo al nivel alto.

•  $t_{p_{HL}}$  = Mide el tiempo transcurrido desde que se produce una transición en la entrada de la puerta, y la salida de la misma comienza a sufrir una transición desde el nivel alto al nivel bajo.

Tal y como se presenta en la figura 3.13, estos tiempos se miden desde el instante en que la señal de entrada ( $V_i$ ) alcanza el 50 % de su valor máximo, hasta el instante en que la señal de salida ( $V_o$ ) alcanza, también, el 50 %.

Para el 74AS04, el fabricante da los valores que se resumen en la tabla 3.8 Tabla 3.8: Características temporales de la puerta 74AS04 según suministra su fabricante.

switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | C <sub>L</sub><br>R <sub>L</sub> | $V_{CC}$ = 4.5 V to 5.5 V,<br>$C_L$ = 50 pF,<br>$R_L$ = 500 $\Omega$ ,<br>$T_A$ = MIN to MAX <sup>†</sup> |      |      | UNIT |

|------------------|-----------------|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|

|                  | (               | (00.1101)      | SN54AS04                         |                                                                                                           | SN74 | AS04 | 1    |

|                  |                 |                | MIN                              | MAX                                                                                                       | MIN  | MAX  |      |

| <sup>‡</sup> PLH | Α.              | V              | 1                                | 6                                                                                                         | 1    | 5    | p.c. |

| t <sub>PHL</sub> | ^               | l '            | 1                                | 4.5                                                                                                       | 1    | 4    | ns   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

En la mayoría de las situaciones no es necesario diferenciar entre  $t_{p_{HL}}$  y  $t_{p_{HL}}$  por lo que se da un único valor de propagación  $t_p$  que se obtiene a partir del valor medio de los dos valores anteriores.

$$t_p = \frac{t_{p_{HL}} + t_{p_{HL}}}{2}$$

Tabla 3.9: Tiempos de transición y propagación de algunas series lógicas.

|              | 74   | 74LS | 74ALS | 74F   | 74HC | 74HCT | 74AC  |

|--------------|------|------|-------|-------|------|-------|-------|

| $t_{LH}$     | 15ns | 13ns | 10ns  | 2.5ns | 7ns  | 7ns   | -     |

| $t_{HL}$     | 10ns | 3ns  | 6ns   | 2.5ns | 7ns  | 7ns   | -     |

| $t_{p_{LH}}$ | 11ns | 8ns  | 4ns   | 3.7ns | 9ns  | 12ns  | 5ns   |

| $t_{p_{HL}}$ | 7ns  | 8ns  | 4ns   | 3.2ns | 9ns  | 12ns  | 4.4ns |