Prueba 1 Curso 2011/2012

ALUMNO:

- 1. Responda las siguientes cuestiones:

- (a) Exprese 41.6<sub>(10)</sub> en base 2 (obtenga 4 cifras decimales).

- Exprese +41.6 y -41.6 en notación complemento a 2 utilizando 8 bits para la parte entera y 3 para la parte fraccionaria. (2 puntos)

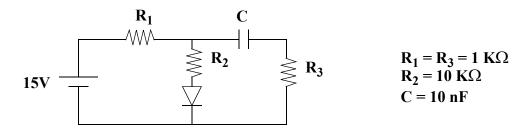

- (b) Para el circuito de la figura, considerando que se ha alcanzado el estado estacionario, obtenga la intensidad que circula por cada rama, la tensión en cada nodo y la carga del condensador. (3 puntos)

- 2. Diseñe un circuito de 4 entradas y 4 salidas. Se trata de un multiplicador binario de dos palabras de 2 bits  $(a_1a_0 \ y \ b_1b_0)$ . Las salidas han de nombrarse:  $z_3$ ,  $z_2$ ,  $z_1$ , y  $z_0$ , siendo  $z_3$  el bit más significativo y  $z_0$  el menos significativo del producto. Se pide:

- (a) el mapa de Karnaugh

- la expresión de z<sub>1</sub> como producto de maxtérminos

- la expresión mínima de z<sub>1</sub> como producto de sumas

- la realización de  $z_1$  mediante el circuito mínimo en dos niveles NOR (2 puntos)

- (b) la realización de  $\mathbf{z_2}$  mediante decodificador con salidas activas en bajo y NAND

- la realización de z<sub>1</sub> mediante MUX 8:1 considerando doble raíl

- la realización de  $z_0$  con MUX 2:1 (2 puntos)

- (c) determine si la siguiente descripción Verilog sería correcta para este multiplicador y justifique si se trata o no de una descripción estructural

```

module multi(

input [1:0] a,

input [1:0] b,

output [3:0] z,

);

assign z = a · b;

endmodule

(1 punto)

```