Última modificación: 21/2/22

IMPORTANTE: Muchos problemas de este boletín aparecen resueltos, total o parcialmente en el libro conocido como "Baena", titulado "PROBLEMAS DE CIRCUITOS Y SISTEMAS DIGITALES" y cuyos autores son Carmen Baena y otros profesores del Departamento de Tecnología Electrónica.

#### Problema 1

Un registro universal (RU8) de 8 bits tiene la siguiente descripción:

- Entradas de datos: 8 en paralelo  $(X_{7-0})$  y dos en serie  $(r \ y \ I)$ , una para desplazamiento a derecha (r) y otra a izquierda (I).

- Salidas de datos: 8 en paralelo (z<sub>7-0</sub>).

- Entradas de control: la del reloj (Ck) y dos para las distintas operaciones ( $S_1S_0$ , con 00 para inhibición, 01 para desplazamiento a la derecha, 10 para desplazamiento a izquierda y 11 para carga en paralelo).

Descríbalo a nivel RT. Especifique un registro equivalente cuyo control se efectúe con sólo una entrada activa por cada operación de cambio de datos. Diséñelo utilizando un RUS

RU8. El problema 1 de este boletín es muy similar al problema 13 de la página 314 del Baena que aparece allí con una solución resumida.

#### Problema 2

Describa a nivel RT un contador ascendente mod-64 con puesta a cero, carga en paralelo e inhibición.

El problema 2 de este boletín es muy similar al problema 11 de la página 313 del Baena, que aparece allí con una solución resumida.

## Problema 3

Se definen las siguientes operaciones de desplazamiento a la derecha:

LSR (Logic Shift Right):

Se trata del llamado desplazamiento lógico, en el que el bit de entrada serie es 0.

- ASR (Arithmetic Shift Right):

Se trata del llamado desplazamiento aritmético, en el que el bit de entrada serie es el bit de signo.

- ROR (Rotation Right):

Se trata de la llamada rotación, en la que el bit de entrada serie coincide con el bit de salida serie.

Describa las tres operaciones a nivel RT para un registro de *n* bits, representando el circuito correspondiente.

El problema 3 de este boletín es parecido al problema 4 de la página 297 del Baena, que aparece allí con una solución detallada.

Problema 4 de este boletín es muy similar al problema 1 de la página 294 del Baena, que aparece allí con una solución detallada.

Compare las siguientes declaraciones RT:

- a) A + B: E  $\leftarrow$  C + D

- b) A + B: E  $\leftarrow$  C  $\vee$  D

- c) C + D: E  $\leftarrow$  A + B

- d)  $A \bullet B: E \leftarrow C \wedge D$

- e) A B: E ← C D

- f) A  $\bullet$  B: E  $\leftarrow$  C x D

Problema 5 de este boletín es muy similar al problema 14 de la página 314 del Baena, que aparece allí con una solución resumida.

Se dispone de un registro con terminales de entrada y salida separados que posee una única señal de control para escritura, W. Se pretende incorporar este registro a un sistema ya dado a través de un bus 3-estados bidireccional. Describa cómo se implementa la incorporación.

Problema 6 de este boletín es muy similar al problema 5 de la página 299 del Baena, que aparece allí con una solución detallada.

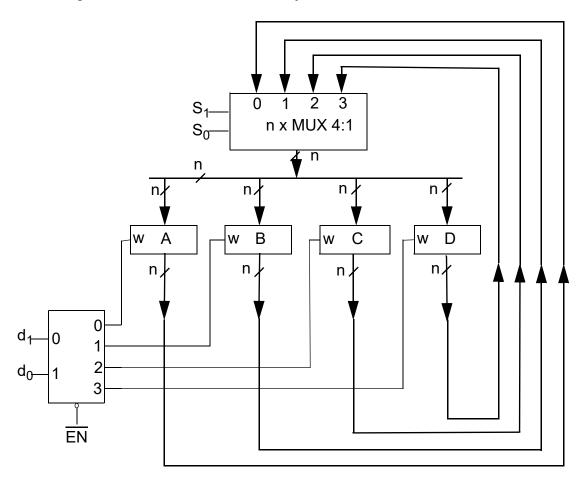

Se dispone de cuatro registros con datos ( $R_0$ ,  $R_1$ ,  $R_2$  y  $R_3$ ) y una ALU, todo de n bits. Se desea diseñar un sistema que permita a cualquiera de los registros ser operandos fuente y/o destino del resultado. El registro fuente del dato A es seleccionado por dos bits,  $A_1$  y  $A_0$ ; el de B, por  $B_1$  y  $B_0$ ; y el de destino, por  $D_1$  y  $D_0$ . Muestre la estructura del sistema e indique cómo se realiza una operación en los siguientes casos:

- 6.1 Un esquema de conexión basado en multiplexado, usando registros con terminales de entrada y salida separados.

- 6.2 Un esquema de conexión basado en buses triestado, usando registros con terminales de entrada y salida separados.

- 6.3 Usando registros con terminales de datos bidireccionales.

Añada, en cada caso, los dispositivos que se necesiten.

Indique, también en cada caso, la secuencia de activación de las señales de control de los dispositivos indicando de dónde provienen.

El problema 7 de este boletín es parecido al problema 15 de la página 315 del Baena, que aparece allí con una solución resumida.

En un sistema digital se desean implementar las siguientes micro-operaciones condicionales:

W: M ← MBR (El dato de MBR se escribe en memoria)

R: MBR  $\leftarrow$  M (Se lee de memoria un dato y se escribe en MBR)

E: MBR ← EXR (Se carga en MBR el dato de un registro externo EXR).

- La memoria M es RAM de 2<sup>k</sup> x n, con bus de datos de entrada y de salida separados, con una señal de habilitación activa en alta (EN) y señal de control de lectura-escritura (R/W); cuando no se lee de la memoria, sus salidas muestran un 0 lógico.

- El registro MBR es de n bits, con entradas y salidas separadas, señal de carga en paralelo (L) y salidas incondicionales.

- El registro EXR, de n bits, tiene salidas incondicionales.

- 7.1 Describa a nivel RT los dispositivos con memoria y construya la unidad de datos del sistema. Las señales W, R y E son generadas por el controlador. No importa cómo se generen las señales de dirección de la memoria.

- 7.2 Proporcione la descripción Verilog de la unidad de datos diseñada en el apartado anterior.

#### Problema 8

Un procesador posee los siguientes registros: un contador de programa (PC) y un registro de direcciones de memoria (MAR) de 16 bits, un registro de datos de memoria (MDR) de 24 bits y un registro de instrucciones (IR) de 8 bits. MAR podrá ser cargado con el contenido de PC (cuando se activa una señal LPC) o con los 16 bits menos significativos de MDR (cuando se activa una señal LMDR). Los 8 MSB de MDR se almacenarán en IR (cuando se active una señal TMDR).

Indique a nivel RT las transferencias hacia MAR y hacia IR, y dibuje un diagrama de bloques del procesador.

El problema 8 de este boletín es parecido al problema 21 de la página 323 del Baena, que aparece allí con una solución resumida.

Problema 9 de este boletín es parecido al problema 2 de la página 294 del Baena, que aparece allí con una solución detallada.

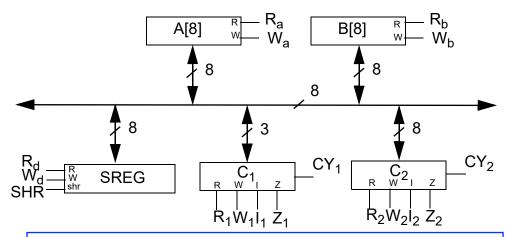

En la unidad de datos de la figura se activan las señales de acuerdo con la siguiente secuencia de control.

| ciclo | EN d <sub>1</sub> d <sub>0</sub> S <sub>1</sub> S <sub>0</sub> |   |   |   |   |  |

|-------|----------------------------------------------------------------|---|---|---|---|--|

| 1     | 0                                                              | 1 | 1 | 0 | 0 |  |

| 2     | 1                                                              | 1 | 1 | 1 | 1 |  |

| 3     | 0                                                              | 0 | 0 | 0 | 1 |  |

| 4     | 0                                                              | 0 | 1 | 1 | 0 |  |

| 5     | 1                                                              | 0 | 0 | 0 | 0 |  |

| 6     | 0                                                              | 1 | 0 | 1 | 1 |  |

|       | i                                                              |   |   |   |   |  |

- 9.1 Proporcione la descripción Verilog de la unidad.

- 9.2 Describa qué operaciones se hacen (a nivel RT), así como la operación global en los seis ciclos de reloj.

Problema 10 de este boletín es parecido al problema 8 de la página 305 del Baena, que aparece allí con una solución detallada.

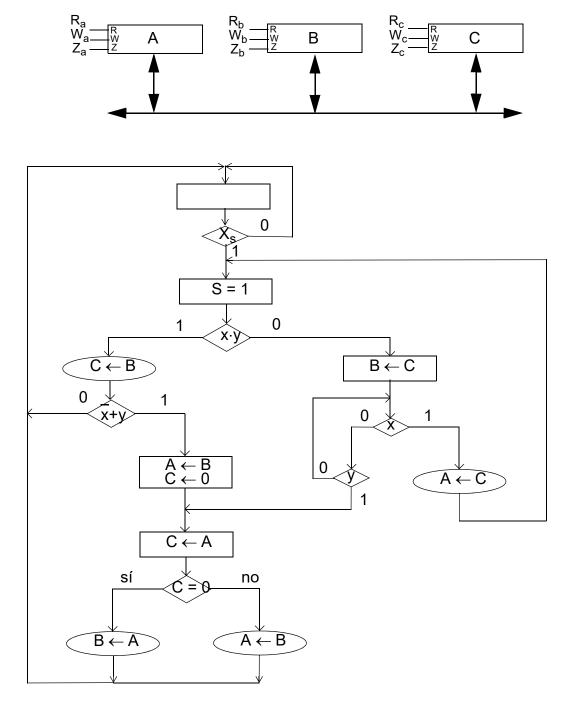

La figura muestra una carta ASM de un sistema así como la unidad de datos correspondiente. En dicha carta, x e y son entradas que pueden tener cualquier valor binario, permaneciendo constantes desde que  $X_s$  se hace 1.

- 10.1 Proporcione la descripción Verilog de la unidad de datos

- 10.2 Especifique todos los errores de la carta, comentándolos brevemente.

Problema 11 de este boletín es parecido al problema 10 de la página 311 del Baena, que aparece allí con una solución detallada.

Considere un sistema con tres registros (A, B, C) de ocho bits. Ha de tener lugar la siguiente secuencia de operaciones en el orden que se describen:

Cuando se activa una señal de comienzo  $(X_s)$ , los datos de entrada se cargan en A. El complemento de los datos de A se cargan en C. A continuación, los datos de C se almacenan en B. Con los datos de A y B se hace la operación OR y el resultado se almacena en C. Finalmente, los datos de C son situados en las líneas de salida, tras lo cual el sistema va al estado de espera.

- 11.1 Describa las operaciones a nivel RT.

- 11.2 Diseñe la unidad de datos que pueda realizarlas.

- 11.3 Haga la carta ASM de las señales a activar por el control.

- 11.4 Proporcione la descripción Verilog de las unidades de datos y de control

- 11.5 ¿Habría que hacer algún cambio para imponer que las líneas de salida estuviesen en alta impedancia cuando no mostraran el dato? En su caso, ¿cuáles son?

#### Problema 12

Se desea realizar la siguiente microoperación:

K

$$T_0$$

A  $\leftarrow$  B<sub>0</sub>

$T_1$  A  $\leftarrow$  B<sub>1</sub>

$T_2$  A  $\leftarrow$  B<sub>2</sub>

$T_3$  A  $\leftarrow$  B<sub>3</sub>

NOR  $(T_0, T_1, T_3, T_4)$  NOP

donde K identifica esta microoperación,  $T_0$ - $T_3$  son las variables de entrada, los registros son de ocho bits y, en cada instante, hay como mucho una señal de entrada a 1 (esto es,  $T_i$ - $T_j$  = 0  $\forall i, j$ ).

- 12.1 Represente el bloque ASM correspondiente.

- 12.2 Muestre una implementación del circuito que realiza esta instrucción en los dos casos siguientes:

- a) Los registros B<sub>i</sub> tienen salida estándar.

- b) Los registros B<sub>i</sub> tienen salida triestado (alta impedancia).

El problema 12 de este boletín es muy similar al problema 19 de la página 320 del Baena, que aparece allí con una solución resumida.

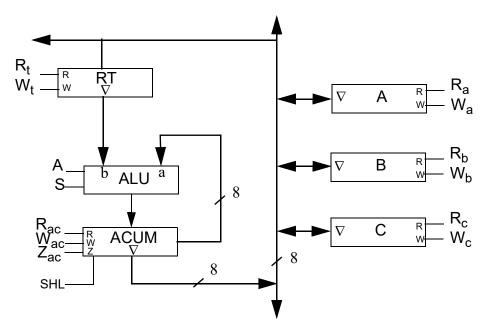

Problema 13 de este boletín es parecido al problema 9 de la página 347 del Baena, que aparece allí con una solución resumida.

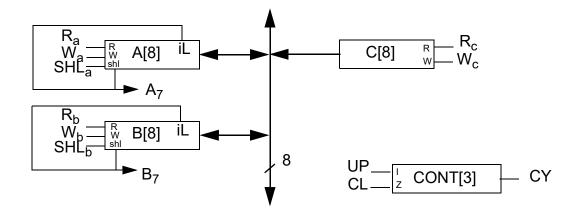

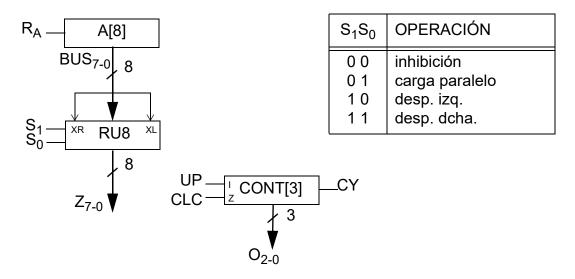

Para la unidad de datos de la figura:

13.1 Obtenga la carta ASM de un controlador que permita realizar la operación de intercambio de información entre los registros A, B, C de la siguiente forma:

$$A \to B \to C$$

13.2 Proporcione la descripción Verilog de las unidades de datos y de control

Problema 14 El problema 14 de este boletín es parecido al problema 10 de la página 348 del Baena, que aparece allí con una solución resumida.

Para la unidad de datos de la figura anterior, obtenga la carta ASM de un controlador que permita realizar la operación siguiente:

$$C = 4 * (A + B)$$

Nota: La entrada SHL del acumulador produce un desplazamiento lógico hacia la izquierda, introduciendo un "0" por la derecha.

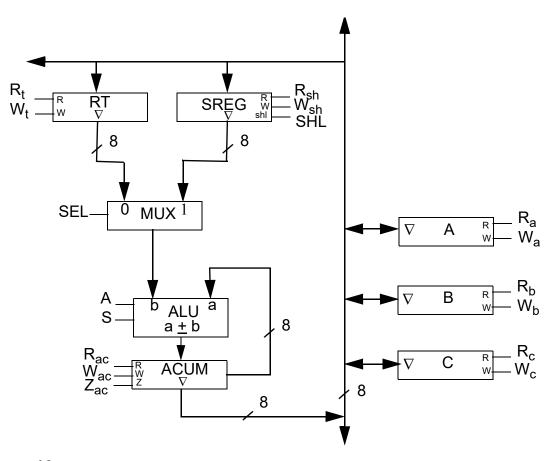

#### Problema 15

Para la unidad de datos de la figura, obtenga la carta ASM una unidad de control de forma que, en función de dos bits de entrada I<sub>1</sub>, I<sub>0</sub>, pueda elegirse entre una de las cuatro macrooperaciones siguientes:

1)

$$A \leftarrow A + 2B$$

3) C

$$\leftarrow$$

A - 2B

2)

$$A \leftarrow A - 2B$$

4) C

$$\leftarrow$$

2A + 2B

El problema 15 de este boletín es parecido al problema 11 de la página 349 del Baena, que aparece allí con una solución resumida.

# Problema 16

Para la unidad de datos de la figura, obtenga la carta ASM de un controlador que permita escribir en B el número de "1" que hay en A. El contador  $C_1$  es de tres bits (mod. 8) y el  $C_2$  de 8 bits (mod. 256). ¿Qué cambio hay que introducir para escribir en B el número de "0" de A?

Nota:  $Z_i$  = Puesta a 0 síncrona,  $I_i$  = Incremento,  $CY_i$  = CARRY.

El problema 16 de este boletín es muy similar al problema 1 de la página 327 del Baena, que aparece allí con una solución detallada.

Pág. 8 de 16

El problema 17 de este boletín es muy similar al problema 13 de la página 353 del Baena, que aparece allí con una solución resumida.

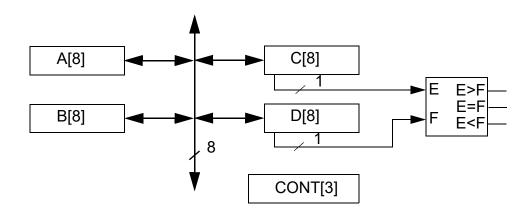

Para la unidad de datos que se presenta, se quiere realizar un sistema digital capaz de comparar dos números de 8 bits (A y B), y almacenar en A el mayor de ellos y en B el menor. Tras finalizar la operación, el sistema generará una señal de FIN.

- 17.1 Defina correctamente las operaciones de los registros.

- 17.2 Obtenga la carta ASM.

- 17.3 Sin añadir elementos nuevos, ¿se puede simplificar la arquitectura de esta unidad de proceso? Razone la respuesta.

Problema 18 de este boletín es muy similar al problema 14 de la página 355 del Baena, que aparece allí con una solución resumida.

La figura muestra la solución al último apartado del problema anterior. Recordemos que se trata de almacenar en A el mayor y en B el menor de los datos previamente almacenados en A y B. Determine la carta ASM para esta unidad.

El problema 19 de este boletín es parecido al problema 12 de la página 351 del Baena, que aparece allí con una solución resumida.

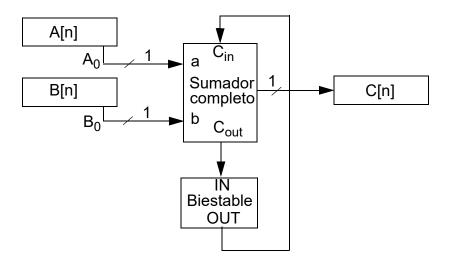

En la unidad de datos de la figura se han representado todos los componentes y los caminos de datos. Suponga que, además, existe disponible una señal, FIN, que se pone a 1 cuando se han sumado n bits. Se desea realizar las tres macrooperaciones siguientes:

$$C \leftarrow A + B$$

$C \leftarrow A$

$C \leftarrow B$

- 19.1 Especifique las señales de control y operaciones de los registros y el biestable.

- 19.2 Obtenga la carta ASM del controlador

- 19.3 Proporcione la descripción Verilog de las unidades de datos y control.

#### Problema 20

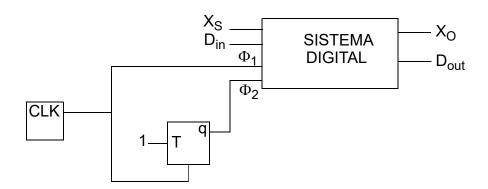

Diseñe un sistema digital (ver figura), que opere como sigue. Sincronizado con  $\emptyset_1$ , recibe por  $X_S$  un pulso de un ciclo de duración y, a continuación, 8 bits de datos en serie por una línea  $D_{in}$ .

El sistema, de forma sincronizada con  $\emptyset_2$ , en primer lugar debe generar por  $X_0$  un pulso de un ciclo de duración y, seguidamente, retransmitir por  $D_{out}$  los 8 bits de datos recibidos.

El problema 20 de este boletín es muy similar al problema 15 de la página 356 del Baena, que aparece allí con una solución resumida.

Problema 21 de este boletín es muy similar al problema 3 de la página 333 del Baena, que aparece allí con una solución detallada.

Un número decimal de dos dígitos se almacena en dos registros de cuatro bits en forma BCD. El registro M contiene los dígitos más significativos; el L, los menos. Los números se transfieren para que aparezcan en un registro R de ocho bits. Para efectuar la transferencia se dispone de un bus de cuatro bits accesible a M y L, pero sólo a las cuatro posiciones de más a la derecha del registro R. La operación de transferencia se realiza respondiendo a un conmutador.

- 21.1 Establezca una arquitectura para el sistema especificando los terminales de control de cada registro.

- 21.2 Construya la carta ASM.

**Problema 22** El problema 22 de este boletín no se corresponde con ninguno del Baena. Haga la carta ASM de un ascensor que circula entre dos pisos ( $1^{\circ}$  y  $2^{\circ}$ ). En cada piso hay un pulsador para llamar al ascensor ( $L_1$  y  $L_2$ ) y dentro del ascensor hay dos pulsadores ( $B_1$  y  $B_2$ ) para elegir el piso de destino. En cada piso existe un sensor que detecta la llegada del ascensor y activa una señal ( $T_1$  para el  $1^{er}$  piso y  $T_2$  para el  $2^{\circ}$ ).

- 22.1 Si el ascensor está en movimiento y se pulsa algún interruptor debe continuar hasta alcanzar el piso destino.

- 22.2 Antes de iniciar el movimiento hay que dar la orden de cerrar la puerta del ascensor (señal CP) y al finalizar el recorrido hay que dar la orden de abrir la puerta (señal AP).

- 22.3 Para que el ascensor se mueva hay que activar las señales SUBE o BAJA hasta que alcance el piso destino.

Problema 23 de este boletín es muy similar al problema 4 de la página 336 del Baena, que aparece allí con una solución detallada.

Un sistema digital tiene como unidad de datos lo representado en la figura. Inicialmente, al menos uno de los bits de A es un cero. El sistema debe dar como salida el número binario de la posición del "0" menos significativo de la palabra almacenada en el registro A.

- 23.1 Describa, a nivel RT, los componentes de esta unidad de datos.

- 23.2 De la carta ASM.

- 23.3 Si el valor inicial de A es: 10101011, represente en el tiempo (hasta que se ha generado la salida deseada) los siguientes parámetros: BUS, señales de control (RA, S<sub>1</sub>, S<sub>0</sub>, CLC, UP) y las salidas del sistema digital.

- 23.4 ¿Cuál es el contenido de RU8 y de CONT tras regresar al estado de espera?

#### Problema 24

Un sistema digital debe analizar su línea de entrada X con objeto de contabilizar el número de pulsos de esa señal que tiene de anchura 1, 2 ó 3 ciclos de reloj. El sistema dispone de tres salidas  $(z_1, z_2, z_3)$  con las que se indica cuál de los tres tipos de pulsos es más numeroso. (Por ejemplo, si se han recibido siete pulsos de un ciclo de reloj, cuatro pulsos de dos ciclos y nueve pulsos de tres ciclos, el sistema generaría como salida  $z_1z_2z_3=001$ ). Desde que se le da la orden de comienzo, se deberán analizar 256 ciclos de reloj, volviéndose después al estado inicial. Diseñe dicho sistema, utilizando los subsistemas habituales.

Nota 1: Nunca se recibirán pulsos de más de tres ciclos de reloj.

Nota 2: En caso de igualdad se activan las salidas correspondientes.

El problema 24 de este boletín es muy similar al problema 6 de la página 340 del Baena, que aparece allí con una solución detallada.

Problema 25 de este boletín es muy similar al problema 7 de la página 343 del Baena, que aparece allí con una solución detallada.

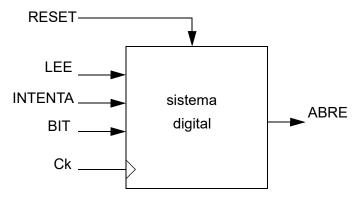

Un sistema digital (ver figura) consiste en una cerradura electrónica que se abre mediante una combinación adecuada de 8 bits. La combinación está almacenada en el sistema. El modo de operación es como sigue:

- La señal RESET lleva al sistema al estado inicial (no hay que incluirla dentro de la carta ASM ya que se considera asíncrona).

- La señal BIT indica el bit correspondiente de la combinación (comenzando por el más significativo).

- La señal LEE (al activarse) indica que se puede leer la entrada BIT.

- La señal INTENTA (al activarse) indica que ya se ha introducido la combinación y si es correcta se abrirá la caja (poniéndose la salida ABRE a 1).

- 25.1 Diseñe la unidad de datos del sistema.

- 25.2 Exprese el algoritmo de control mediante una carta ASM.

Problema 26 El problema 26 de este boletín no se corresponde con ninguno del Baena.

Se desea diseñar la unidad de control del nuevo modelo de lavadora V-1000 que tiene las siguientes especificaciones:

- El ciclo de lavado, que se inicia al activar la orden de comienzo Xs, consta de prelavado (P), lavado (L), aclarado (A) y centrifugado (C), que se harán en ese orden. La máquina procederá a cada operación cuando la unidad de control active la correspondiente señal (P, L, A o C).

- La lavadora V-1000 dispone, fuera de la unidad de control, de un contador con señales de puesta a cero (CLS) y de incremento (I), así como cuatro salidas que se activan cuando transcurre el tiempo de prelavado ( $T_P$ ), el de lavado ( $T_L$ ), el de aclarado ( $T_A$ ) y el de centrifugado ( $T_C$ ). Cada uno de estos tiempos ( $T_C$ ,  $T_A$ ,  $T_L$  y  $T_P$ ) se contabilizan desde cero.

- El ciclo de lavado se divide en dos subciclos. Uno de duración fija  $T_L$  y otro variable que termina cuando se activa un "Sensor de Ropa Limpia" (SRL = 1).

- Durante el prelavado, lavado y aclarado la puerta de la lavadora deberá estar bloqueada, para lo cual se activará la salida correspondiente.

- El último ciclo, el de centrifugado, tiene una duración T<sub>C</sub>. Si se detecta la apertura de la puerta de la lavadora, el centrifugado quedará interrumpido. Para ello existirá una señal (PA) que se activa cuando la puerta está abierta. En el momento que se detecta la desactivación de dicha señal, el proceso de centrifugado continuará a partir de donde se interrumpió.

Dibuje el diagrama de bloque y la carta ASM de la unidad de control .

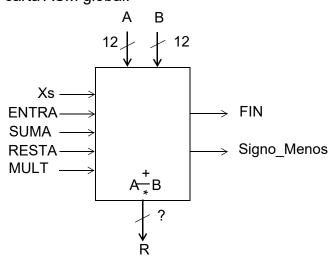

Problema 27 El problema 27 de este boletín no se corresponde con ninguno del Baena. Se desea diseñar una calculadora que realice la suma, resta o multiplicación de dos datos de entrada sin signo de 12 bits (ver figura). Para ello, su diseño se descompondrá en dos partes.

1) Realización de SUMA y RESTA.

Los dos datos de entrada se captarán tras activarse la señal ENTRA. Después, el sistema operará según cuál de las dos señales (SUMA o RESTA) esté activa. Sólo una de estas señales podrá estar activa. El resultado se mostrará en el bus de salida R. Si A<B, al ejecutar RESTA se hará B-A y se activará la salida Signo\_Menos.

- 27.1 Diseñe una unidad de datos propia para este problema. Esto es, no tiene por qué parecerse a la dada en teoría. En todo caso, deberá estar especificada y dimensionada adecuadamente.

- 27.2 Determine la carta ASM.

- 2) Además, realización de MULT.

Al sistema anterior se incorporará la multiplicación A \* B, cuando se active MULT, que se hará sumando A tantas veces como indique B.

- 27.3 Rediseñe la unidad de datos anterior para incorporar esta nueva operación (la unidad de datos no puede incluir un multiplicador como subsistema). Redimensione la unidad para que no existan problemas de desbordamiento.

- 27.4 Obtenga la carta ASM global.

# Problema 28 El problema 28 de este boletín no se corresponde con ninguno del Baena.

Se va a calcular el producto aritmético P de dos números X e Y (P = X·Y). Para ello se van a emplear tres contadores CX, CY y CP. Al comienzo del proceso se cargan los operandos X e Y en sus respectivos contadores CX y CY. El contador CP contendrá el resultado al final del proceso. El producto se obtiene incrementando CP un total de P veces. Para conseguir esto se decrementa CX hasta que llega a cero en cuyo caso se decrementa una vez CY y se vuelve a cargar X en CX. Naturalmente, cuando CY llega a cero CX se ha decrementado un total de X·Y veces. Si al mismo tiempo se ha ido incrementando CP tendremos en ese contador el resultado esperado.

- 28.1 Describa a nivel RT CX, CY y CP.

- 28.2 Obtenga la carta ASM del sistema.

Problema 29 El problema 29 de este boletín no se corresponde con ninguno del Baena.

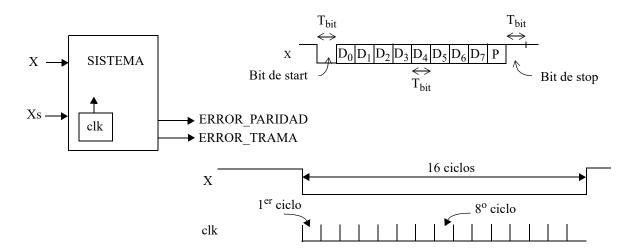

Un formato asíncrono para transmitir en serie un carácter de 8 bits  $(D_0-D_7)$  se muestra en la siguiente figura. El primer bit, que sirve para avisar al receptor del inicio del carácter (bit de start), es un 0 lógico. A continuación vienen los 8 bits del dato, empezando por el menos significativo, el  $D_0$ . Posterior al  $D_7$  viene el bit de paridad impar P y, por último, un bit de stop que es 1 lógico. La duración de cada uno de estos bits es  $T_{\rm bit}$ .

Se desea diseñar un sistema digital capaz de recoger los bits de datos en este formato y almacenarlos en el registro RCREG. El reloj del sistema es mucho más rápido que la señal X; en concreto, el periodo es de T<sub>bit</sub>/16, esto es, existen 16 ciclos de reloj por cada bit de entrada. Tras la activación de la señal Xs el sistema operará de la forma siguiente:

- Si en un ciclo de reloj el sistema detecta X = 0, espera 8 ciclos (punto medio de un bit) y vuelve a leer X. Si ahora X = 1 interpreta que ha habido un error transitorio y vuelve a

esperar un bit de start correcto. Si X sigue valiendo 0 pasa a leer el mensaje para lo cual capturará cada bit leyendo X en el medio del bit (aproximadamente el ciclo octavo (ver figura)).

- Tras leer un dato, el sistema esperará uno nuevo sin necesidad de activarse la señal Xs. Así mismo, el sistema debe activar la señal ERROR\_PARIDAD cuando la paridad recibida no sea la correcta y debe activar la señal ERROR\_TRAMA cuando el bit de stop es un 0 en lugar de un 1.

Diseñe el sistema digital completo.