Última modificación: 20. Feb. 2017

#### Problema 1

Describa la función f= a' b + c d' en Verilog utilizando las tres descripciones posibles: funcional, estructural y procedimental.

#### Problema 2

Repita el ejercicio anterior para f= abc + a b'c' + a' b c'.

#### Problema 3

Describa en Verilog un decodificador de 3:8 con salidas activas en alto. Utilice descripción funcional y procedimental.

#### Problema 4

¿Qué modificaciones habría que realizar en el código Verilog del problema 3 para incorporar señal de habilitación activa en bajo? ¿Y para que las salidas sean también activas en bajo?

#### Problema 5

Se desea utilizar la descripción procedimental para implementar un codificador de prioridad de 4:2 que responda a la siguiente tabla de verdad.

| Io | l <sub>1</sub> | I <sub>2</sub> | I <sub>3</sub>   | $Q_1$ | $Q_{o}$ | E <sub>o</sub> |

|----|----------------|----------------|------------------|-------|---------|----------------|

| 0  | 1              | 1              | 1                | 0     | 0       | 0              |

| X  | 0              | 1              | 1                | 0     | 1       | 0              |

| X  | X              | 0              | 1                | 1     | 0       | 0              |

| X  | X              | X              | 0                | 1     | 1       | 0              |

| 1  | 1              | 1              | 1<br>1<br>1<br>0 | 0     | 0       | 1              |

#### Problema 6

Describa un convertidor BCD a 7-segmentos en Verilog.

#### Problema 7

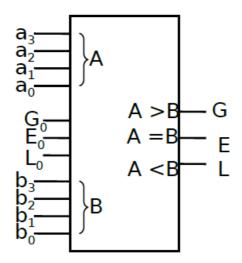

Describa un comparador de magnitudes de 4 bits, como el que se muestra a continuación, utilizando una descripción procedimental.

#### Problema 8

Utilizando tanto las descripciones funcional como procedimental, escriba el código Verilog de un MUX 4:1

#### Problema 9

Describa en Verilog un sumador/restador de n bits.

#### Problema 10

Una ALU de 4 bits implementa las funciones que se recogen en la siguiente tabla. Escriba el código Verilog de dicha ALU.

| S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Función ALU  |                     |

|----------------------------------------------|--------------|---------------------|

|                                              | $C_{in} = 0$ | C <sub>in</sub> = 1 |

| 0 0 0                                        | F = A        | F = A + 1           |

| 0 0 1                                        | F = A + B    | F = A + B + 1       |

| 0 1 0                                        | F = A + B'   | F = A + B' + 1      |

| 0 1 1                                        | F = A - 1    | F = A               |

| 1 0 0                                        | F = A AND B  |                     |

| 1 0 1                                        | F = A OR B   |                     |

| 1 1 0                                        | F = NOT A    |                     |

| 1 1 1                                        | F = A XOR B  |                     |

Utilizando el módulo descrito en el problema 10, construya una ALU de 12 bits en Verilog utilizando la descripción estructural.

#### Problema 12

Describa en Verilog un registro de 8 bits con la siguiente tabla de operación.

| CL LD | Operación          | Tipo      |

|-------|--------------------|-----------|

| 0 x   | REG ← 0            | asíncrona |

| 11    | $REG \leftarrow X$ | síncrona  |

| 10    | REG ← REG          | síncrona  |

#### Problema 13

Describa en Verilog un registro de desplazamiento con la siguiente tabla de operación.

| CL SHR | Operación                        | Tipo      |

|--------|----------------------------------|-----------|

| 0 x    | REG ← 0                          | asíncrona |

| 11     | $REG \leftarrow SHR(REG, X_{R})$ | síncrona  |

| 10     | REG ← REG                        | síncrona  |

#### Problema 14

Describa en Verilog un registro universal de 8 bits con las siguientes operaciones

| CL LD SHR SHL | Operación                                                       | Tipo   |

|---------------|-----------------------------------------------------------------|--------|

| 0 x x x       | REG ← 0                                                         | asínc. |

| 11xx          | REG ← X                                                         | sínc.  |

| 101x          | REG ← SHR(REG, $X_R$ )                                          | sínc.  |

| 1001          | $\begin{array}{c} REG \leftarrow \\ SHL(REG,X_{L}) \end{array}$ | sínc.  |

| 1000          | REG ← REG                                                       | sínc.  |

#### Problema 15

Describa un contador 4 bits con la siguiente tabla de operación.

| CL | Operación                                 | Tipo   |

|----|-------------------------------------------|--------|

| 1  | CONT ← 0                                  | asínc. |

| 0  | $  CONT \leftarrow CONT + 1  _{mod \ 16}$ | sínc.  |

#### Problema 16

Describa un contador de 4 bits con la siguiente tabla de operación y salida de Cy.

| CL EN | Operación                              | Tipo  |

|-------|----------------------------------------|-------|

| 1 x   | CONT ← 0                               | sínc. |

| 01    | $CONT \leftarrow CONT + 1 _{mod \ 16}$ | sínc. |

| 0 0   | CONT ← CONT                            | sínc. |

#### Problema 17

Escriba el código Verilog de un contador módulo-16 con la siguiente tabla de operación.

| LD EN | Operación                              | Tipo  |

|-------|----------------------------------------|-------|

| 1 x   | CONT ← X                               | sínc. |

| 0 1   | $CONT \leftarrow CONT + 1 _{mod \ 16}$ | sínc. |

| 0.0   | CONT ← CONT                            | sínc. |

#### Problema 18

Escriba el código Verilog de un contador módulo-10.

| EN | Operación                           | Tipo  |

|----|-------------------------------------|-------|

| 1  | $CONT \leftarrow CONT+1 _{mod\ 10}$ | sínc. |

| 0  | CONT ← CONT                         | sínc. |

#### Problema 19

Describa un contador descendente de n bits con salida de borrow.

| CL EN | Operación                        | Tipo  |

|-------|----------------------------------|-------|

| 1 x   | CONT ← 0                         | sínc. |

| 0 1   | CONT ← CONT-1  <sub>mod 16</sub> | sínc. |

| 0 0   | CONT ← CONT                      | sínc. |

**Problema 20**Describa un contador reversible de 4 bits con la siguiente tabla de operación.

| CL EN UD | Operación                           | Tipo   |

|----------|-------------------------------------|--------|

| 1 x x    | CONT ← 0                            | asínc. |

| 0 0 x    | CONT ← CONT                         | sínc.  |

| 0 1 0    | $CONT \leftarrow CONT+1 _{mod\ 16}$ | sínc.  |

| 0 1 1    | $CONT \leftarrow CONT-1 _{mod\ 16}$ | sínc.  |

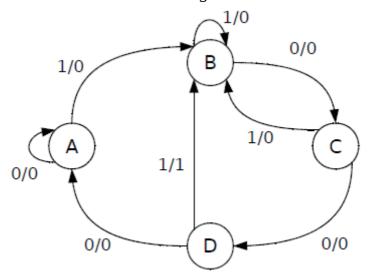

Describa la siguiente FSM usando Verilog.

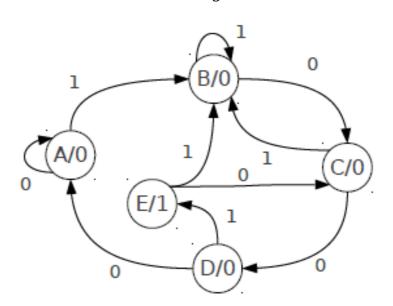

**Problema 22**Describa la siguiente FSM usando Verilog

#### Problema 23

Describa la siguiente FSM usando Verilog

| s <sup>X</sup> | 0                  | 1                  |  |

|----------------|--------------------|--------------------|--|

| $E_0$          | E <sub>0</sub> ,00 | E <sub>1</sub> ,00 |  |

| $E_1$          | E <sub>2</sub> ,00 | E <sub>1</sub> ,01 |  |

| $E_2$          | E <sub>2</sub> ,10 | E <sub>3</sub> ,10 |  |

| $E_3$          | $E_0,10$           | E <sub>3</sub> ,11 |  |

| ,              | NS, Y,Z            |                    |  |

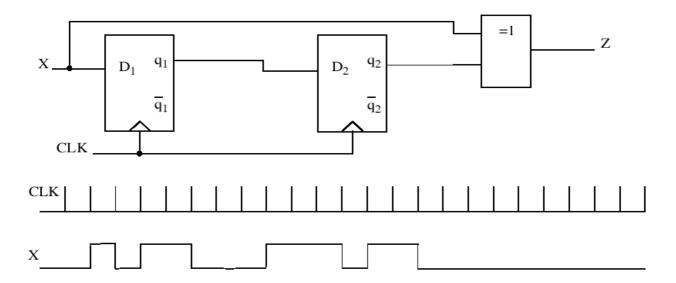

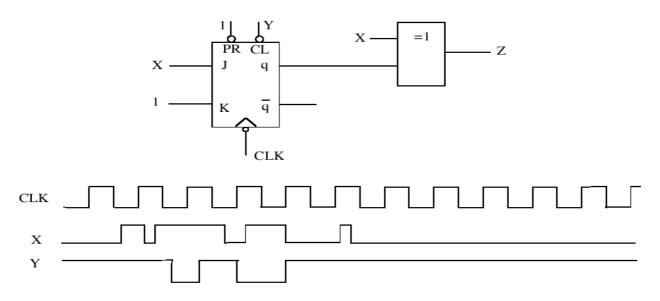

**Problema 24** Describa el siguiente circuito utilizando código Verilog. Emplee descripción procedimental para los biestables y estructural para el conjunto. Obtenga la salida z para la secuencia de entrada que se muestra, para ello cree el fichero de test que permita su simulación.

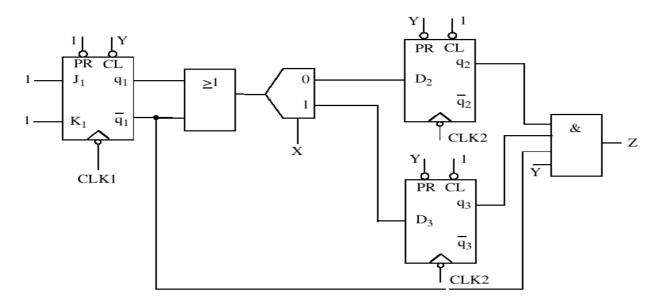

Repita el ejercicio anterior para el siguiente esquemático.

#### Problema 26

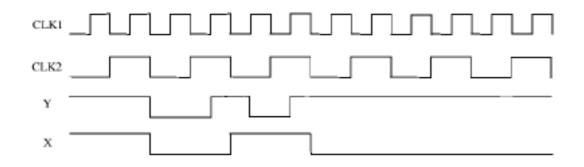

Describa en Verilog el siguiente circuito y obtenga el fichero de test necesario para su simulación, utilizando las secuencias de entradas que se muestran en la figura.

### Problema 27

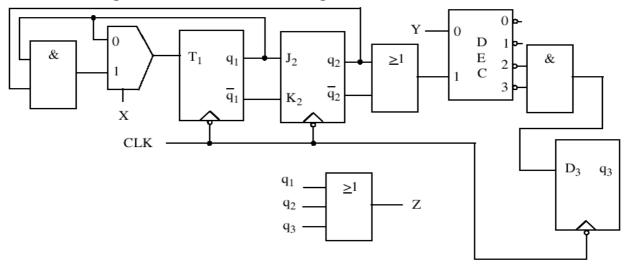

Describa el siguiente circuito en Verilog.

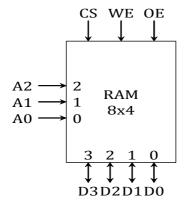

Problema 28 Describa la siguiente RAM en Verilog

Indique qué dispositivo se describe a continuación y de su tabla de verdad.